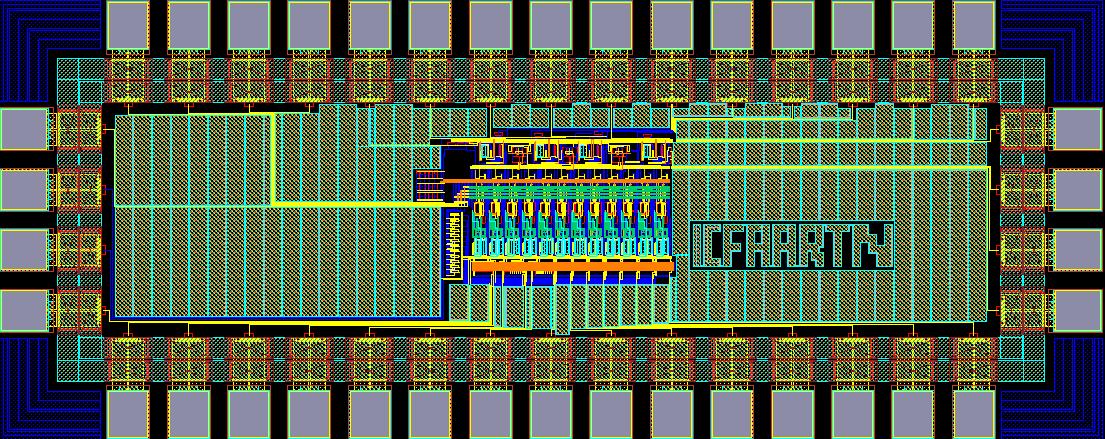

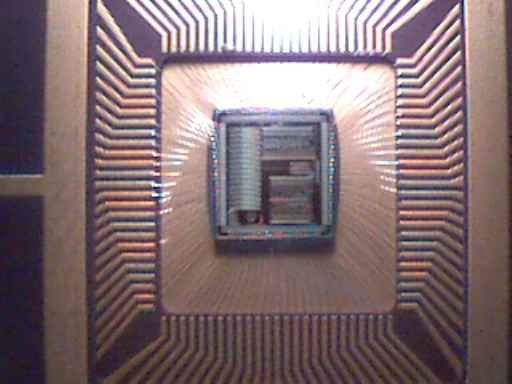

Pierwszy chip realizowany we współpracy z Politechniką Gdańską w 2000 roku. Każdy projektował oddzielne bloki. Moja część (blok na górze) to filtr z przełączanymi pojemnościami Gillinghama. Układ w 95% analogowy (około 500 tranzystorów). Zastosowanie układu to filtr kanałowy pasma podstawowego toru odbiorczego telefonii komórkowej GSM.

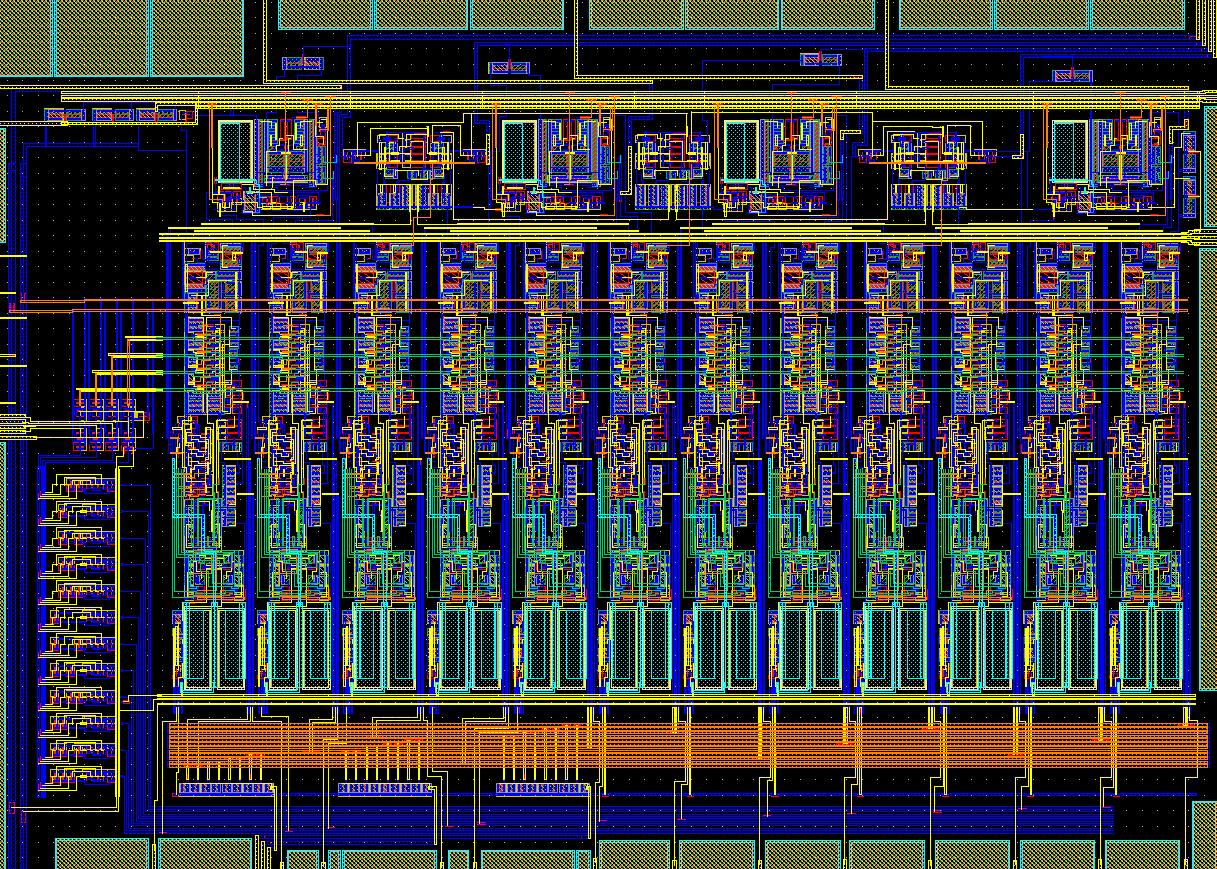

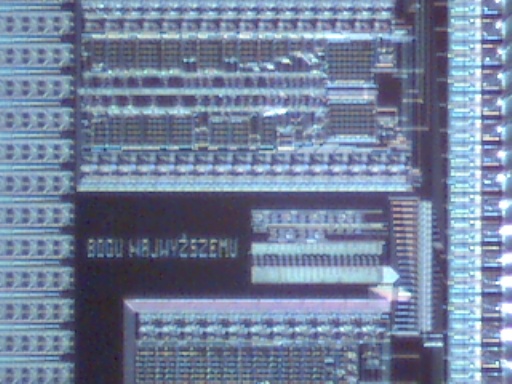

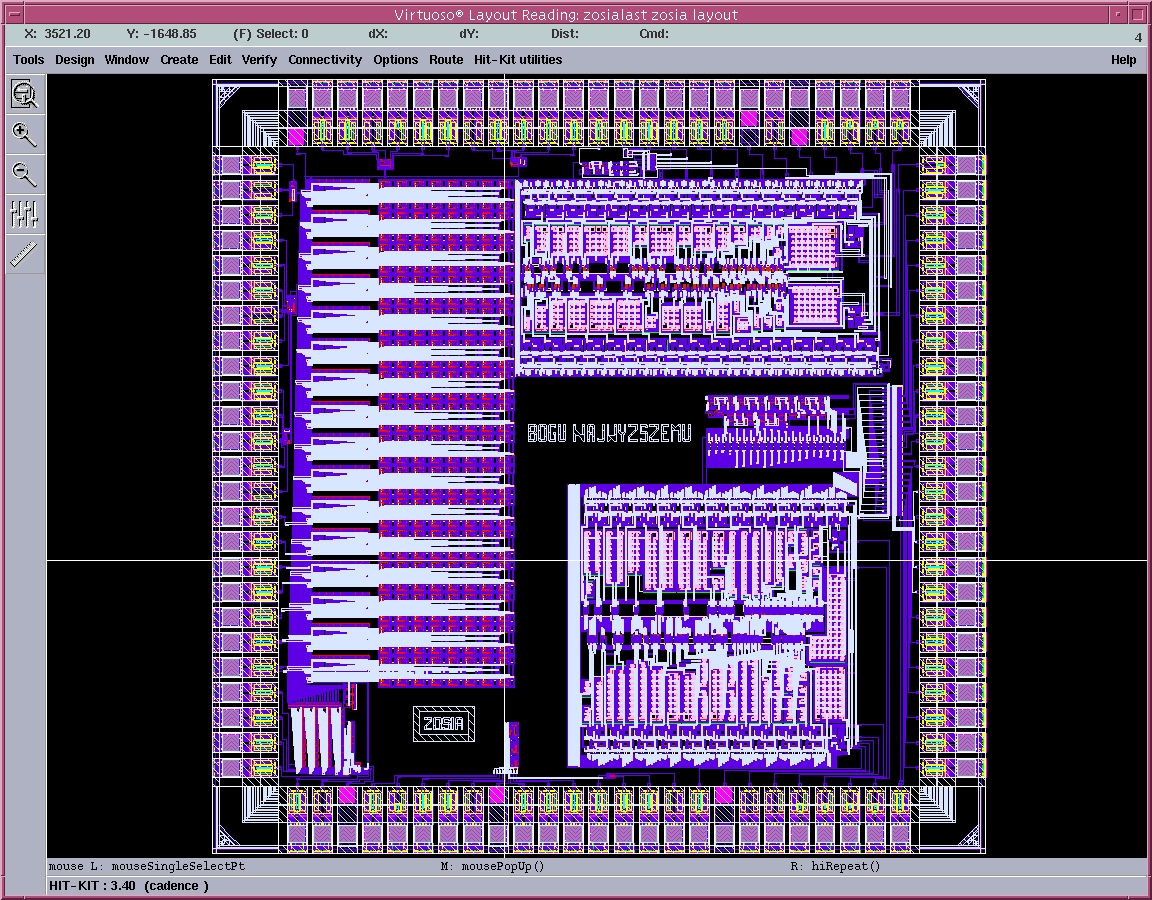

Drugi chip realizowany we współpracy z Uniwersytetem Techniczno-Przyrodniczym (dawna Akademia Techniczno-Rolnicza) w Bydgoszczy w 2002 roku. Chip zawierał osobne bloki, które stały się częścią mojego doktoratu oraz doktoratu kolegi Piotra Grada z Bydgoszczy. Moje bloki to te z prawej. Filtr Gillinghama z poprawkami (pierwsza wersja miała błąd i pół chipu nie działało) oraz filtr even-odd. Oba w technice SC. Układ w 90% analogowy (około 2500 tranzystorów). Zastosowanie układu to filtr kanałowy pasma podstawowego toru odbiorczego telefonii komórkowej GSM.

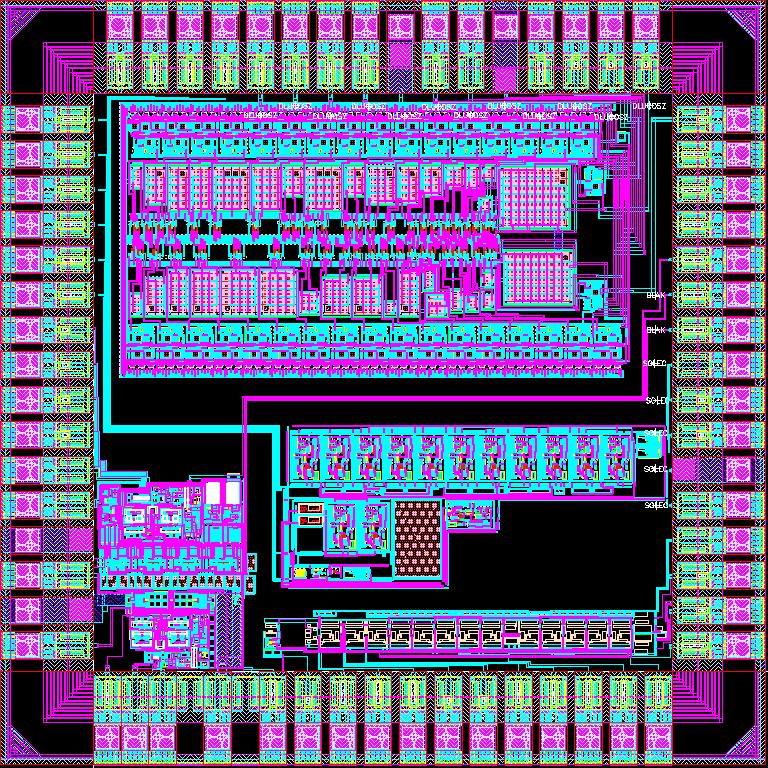

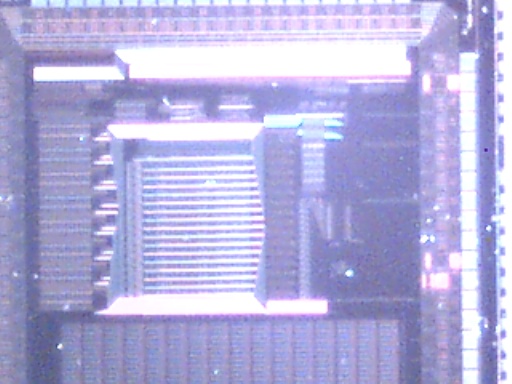

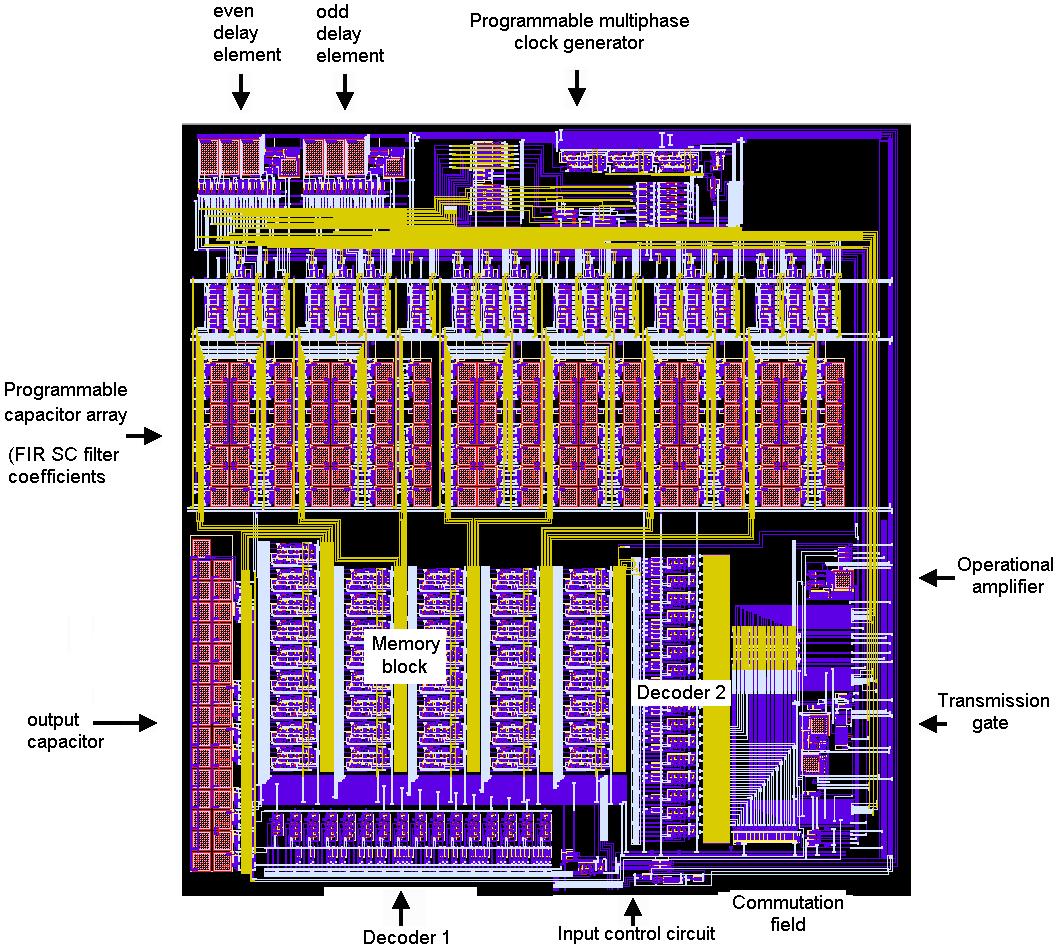

Trzeci chip realizowany we współpracy z Uniwersytetem Techniczno-Przyrodniczym (dawna Akademia Techniczno-Rolinicza) w Bydgoszczy w 2002 roku. Chip zawierał osobne bloki moje i Piotra Grada z Bydgoszczy. Moje bloki to programowalny filtr SC z kluczem rotacyjnym oraz różne inne eksperymentalne bloczki. Realizowany w 2003 roku. Układ w 80% analogowy (około 5000 tranzystorów). Zastosowanie układu to filtr kanałowy pasma podstawowego toru odbiorczego telefonii komórkowej GSM i WCDMA.

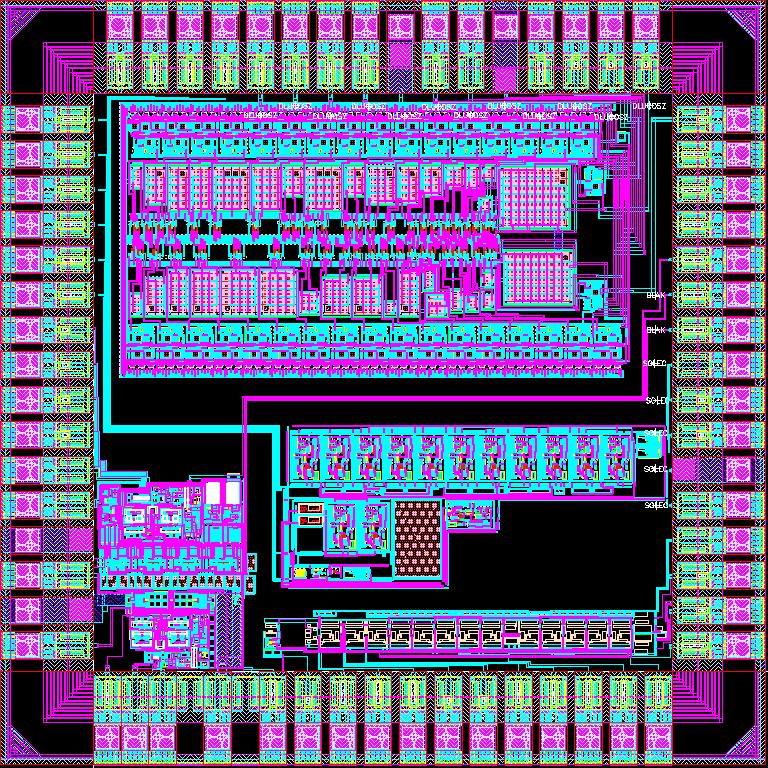

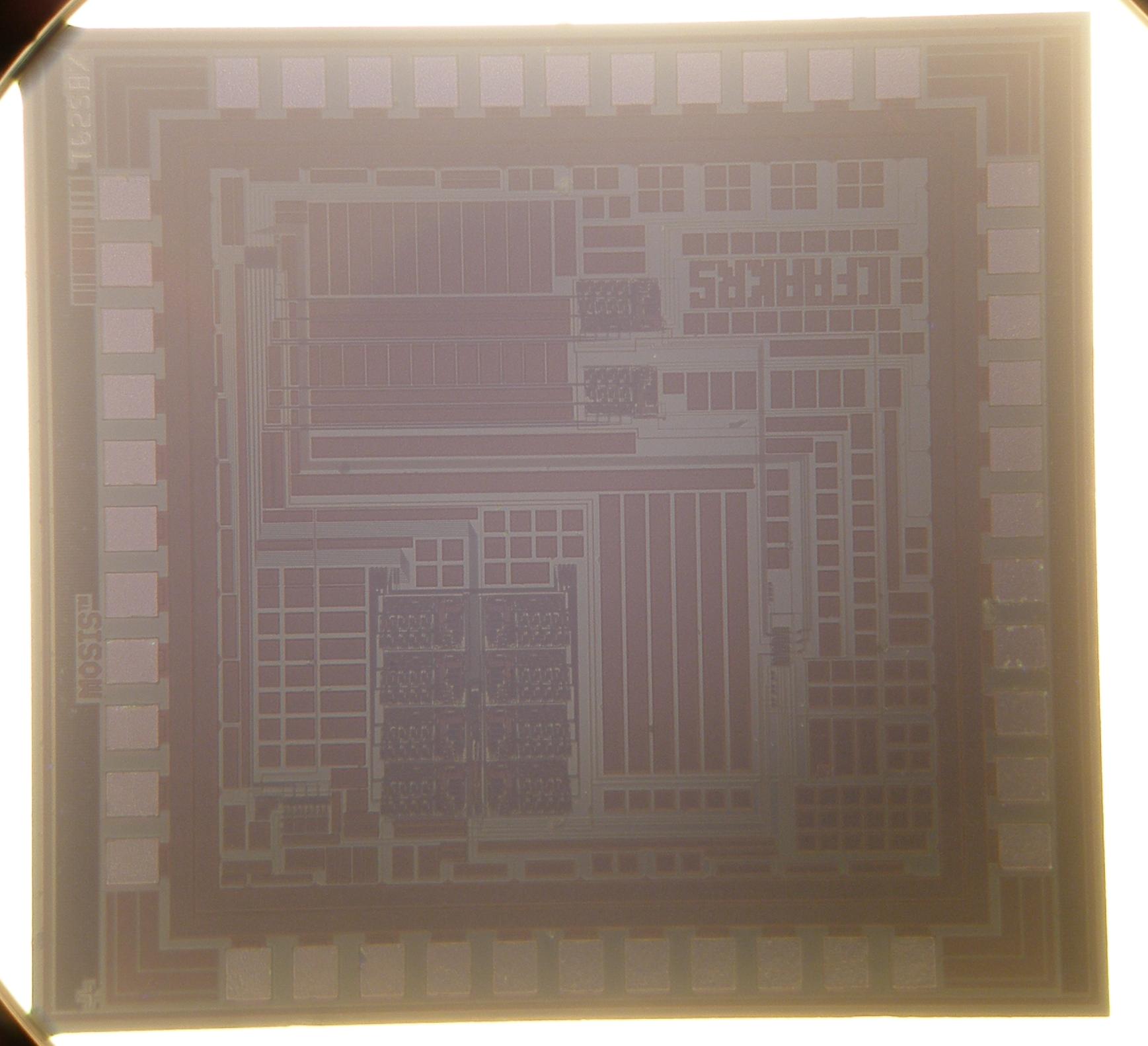

Czwarty chip realizowałem w ramach europejskiego programu Reason, którego kierownikiem był Prof. dr hab. inż. Wiesław Kuźmicz z Politechniki Warszawskiej. Cały chip to układ do celów edukacyjnych. Moja część do filtr programowalny even-odd (technika SC). Układ ma tą właściwość, że można programowo rozłączyć wszystkie bloki i mierzyć je osobno lub zbudować z nich cały filtr programowalny. Zastosowanie z laboratorium układów scalonych. Realizacja 2003 i później jeszcze drobiazgi w 2004 r. Układ w 70% analogowy (około 2500 tranzystorów).

Wszystkie chipy poniżej zrealizowane zostały w czasie stypendium w Kanadzie.

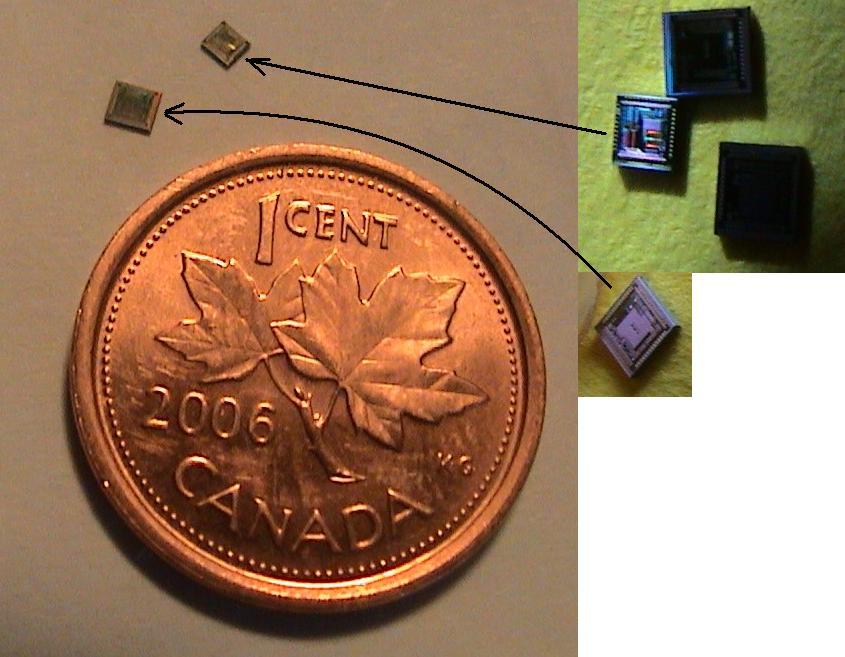

Piąty chip realizowany we współpracy z Tomkiem Talaśką z Uniwersytetu Techniczno-Przyrodniczego w Bydgoszczy na przełomie 2005/2006 roku. Chip zawiera układ sieci neuronowej Kohonena, bez algorytmu uczenia. Układ zawiera również szereg bloków takich jak pamięci analogowe, wtórniki zaprojektowane przez Prof. dr. hab. inż. Ryszarda Wojtynę z UTP. Na pierwszym zdjęciu oba chipy. Układ w 95% analogowy (około 500 tranzystorów).

Szósty chip realizowany na przełomie roku 2005/2006. Chip zawiera przetworniki analogowo-cyfrowe ultra niskiej mocy (kilka uW) oraz filtr analogowy wykonany w technice przełączanych prądów (SI), również bardzo małej mocy poniżej 1uW. Układ w 95% analogowy (około 10000 tranzystorów). Bloki te projektowane są dla urządzeń zwanych Wireless Sensor Networks, albo inaczej Smart Dust. Celem tych urządzeń to tworzenie sieci, gdzie każdy węzeł pracując z ultra niskim poborem mocy jest w stanie sam pobierać energię z otoczenia. Poszczególne węzły mają zdolność komunikacji bezprzewodowej między sobą lub np. ze stacja bazową.

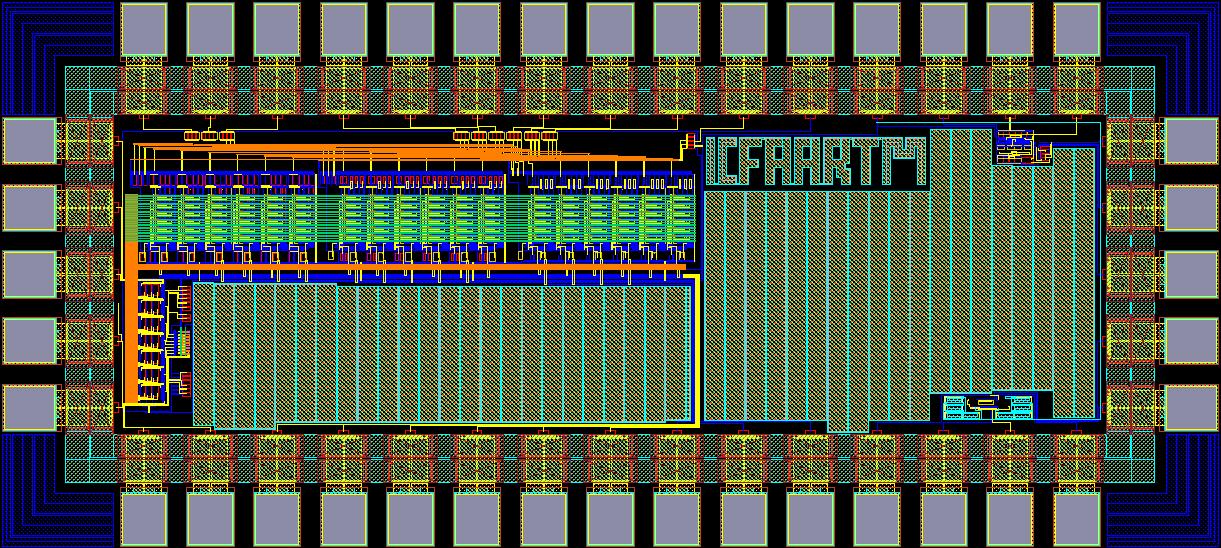

Siódmy układ to wykonany w lipcu 2007 asynchroniczny (bez układu zegara sterującego) programowalny procesor obrazu, umożliwiający równoległe przetwarzanie sygnałów (pikseli) wejściowych. Wykonałem trzy wersje tego procesora w tym układzie. Filtr obrazu oparty jest na układach mnożących Gilberta, pracujących w zakresie podprogowym, gdzie duże znaczenie zaczynają nabierać wpływy niedopasowania tranzystorów w lustrach prądowych. Każda z tych trzech wersji robi dokładnie to samo, ale ma różne wymiary tranzystorów by zbadać wpływ tych niedokładności na precyzje filtru. Jest to o tyle ważne, że pozwoli to ustalenie możliwej do uzyskania głębi barw obrazów wyjściowych. Docelowe zastosowanie układu to systemy wizyjne stosowane np. w robotach mobilnych, lub w mikroukładach stosowanych np. w gastroskopii. W takim przypadku zamiast badać przewód pokarmowy metodą tradycyjną będzie można zastosować kapsułę, którą będzie można połknąć. System taki będzie wykonywał zdjęcia, dokonywał ich obróbki i przesyłał bezprzewodowo do komputera na zewnątrz do analizy.

Układ zawiera dodatkowo bloki kilku innych zespołów badawczych. Układ w 90% analogowy (około 2000 tranzystorów).

Ósmy układ to w pełni programowalna sieć neuronowa z wbudowanym algorytmem uczenia. Układ zawiera cztery neurony, trzy wejścia oraz cztery wyjścia. Najbardziej złożony układ w mojej historii. Układ wykonany w ścisłej kooperacji z Tomkiem Talaśką z Bydgoszczy. W zasadzie wszystkie bloki w układzie zostały zaprojektowane od podstaw. Układ zawiera wiele inetersujących podukładów, jak np. mechanizm karania neuronów, które za często wygrywają rywalizację. Układ jak w zasadzie większość wykonanych przez nas w technologii 0.18um, pracuje w trybie prądowym. Układ w 95% analogowy (około 3000 tranzystorów). Docelowe zastosowanie układu to aplikacje medyczne, min. układ do automatycznego rozpoznawania stanów zawałowych. Pierwsze eksperymenty dały bardzo pozytywne wyniki. Docelowo powstanie sieć zawierająca kilkadziesiąt albo może nawet kilkaset neuronów. Prawdopodobnie na wiosnę 2008 roku.