#### Poznań University of Technology

#### Department of Computing and Management

Institute of Control and System Engineering

# Design and optimization of finite impulse response electronic filters integrated in the CMOS technology

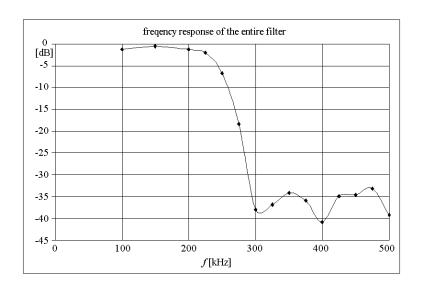

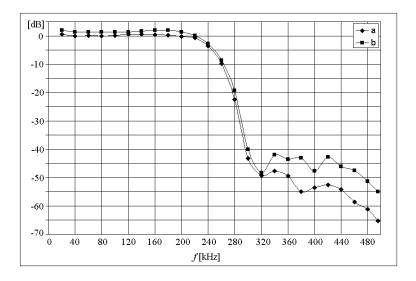

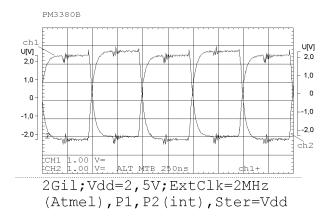

Ph. D. Dissertation

Author: Rafal Długosz

Conferring Professor (promoter): Prof. dr hab. inż. Adam Dąbrowski

Poznań 2004

to Jesus Christ my God and Saviour

# Contents

|   | List                                                                                   | of syn   | mbols and abbreviations                                            | 5  |  |

|---|----------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------|----|--|

| 1 | Inti                                                                                   | roducti  | ion                                                                | 7  |  |

|   | 1.1                                                                                    | Resear   | rch area                                                           | 7  |  |

|   | 1.2                                                                                    | Aim a    | nd scientific thesis                                               | 10 |  |

| 2 | Ger                                                                                    | neral cl | haracteristic of switched capacitor circuits                       | 12 |  |

|   | 2.1                                                                                    | Basics   | s of the SC technique                                              | 12 |  |

|   | 2.2                                                                                    | Buildi   | ng blocks of the SC FIR filters                                    | 13 |  |

|   |                                                                                        | 2.2.1    | SC memory elements                                                 | 13 |  |

|   |                                                                                        | 2.2.2    | SC summer circuits                                                 | 16 |  |

|   | 2.3                                                                                    | Theor    | etical SC FIR filter architectures                                 | 17 |  |

|   |                                                                                        | 2.3.1    | Basic SC FIR filter structures                                     | 17 |  |

|   |                                                                                        | 2.3.2    | Composite SC FIR filter structures                                 | 18 |  |

|   |                                                                                        | 2.3.3    | Diagrams of the basic and composite SC FIR filter structures $$ .  | 20 |  |

| 3 | Cor                                                                                    | nparis   | on and evaluation of the SC FIR filter structures                  | 30 |  |

|   | 3.1                                                                                    | Evalua   | ation of the chip area on the basis of theoretical assumptions     | 31 |  |

|   |                                                                                        | 3.1.1    | Chip area estimation                                               | 31 |  |

|   |                                                                                        | 3.1.2    | Number of elements as a function of the filter order $N$           | 32 |  |

|   |                                                                                        | 3.1.3    | Conclusions                                                        | 37 |  |

|   | 3.2 Evaluation of the chip area on the basis of the real values of filter coefficients |          |                                                                    |    |  |

|   |                                                                                        | 3.2.1    | Influence of the frequency response of the filter on the chip area | 39 |  |

|   |                                                                                        | 3 9 9    | Chin area evaluation                                               | 44 |  |

|   | 3.3                           |             | arison of the SC FIR filter structures on the basis of the clock a criteria   | 48   |  |  |

|---|-------------------------------|-------------|-------------------------------------------------------------------------------|------|--|--|

|   |                               | 3.3.1       | Theoretical clock systems for particular SC FIR filters                       | 48   |  |  |

|   |                               | 3.3.2       | Practical aspects of realization of clock systems                             | 51   |  |  |

|   | 3.4                           | Compa       | arison of SC FIR filter structures on the basis of power consumption          | ı 56 |  |  |

|   | 3.5                           | Compa       | arison of SC FIR filter structures on the basis of signal quality             | 56   |  |  |

|   | 3.6                           | New fa      | amily of even-odd delay line structures                                       | 57   |  |  |

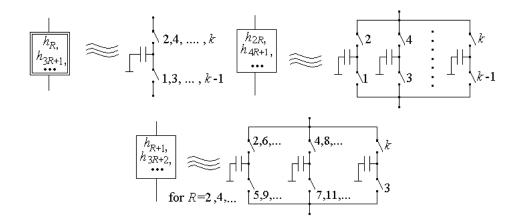

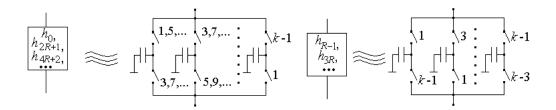

|   |                               | 3.6.1       | Even and odd delay elements                                                   | 57   |  |  |

|   |                               | 3.6.2       | Even-odd delay line structures                                                | 60   |  |  |

|   |                               | 3.6.3       | Theoretical evaluation of the chip area of the even-odd delay line structures | 63   |  |  |

| 4 | $\mathbf{C}\mathbf{M}$        | OS rea      | alization of the chosen SC FIR filter structures                              | 67   |  |  |

|   | 4.1                           | Specifi     | cation of the GSM channel filter                                              | 68   |  |  |

|   | 4.2                           | Buildi      | ng blocks of SC FIR filters                                                   | 74   |  |  |

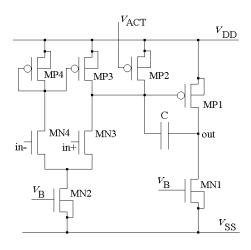

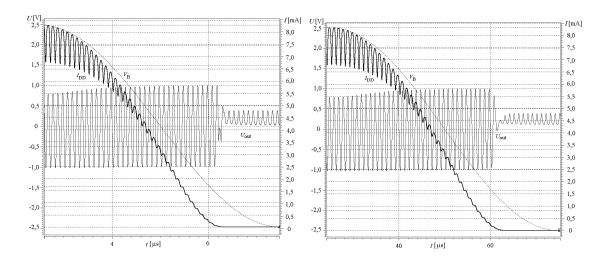

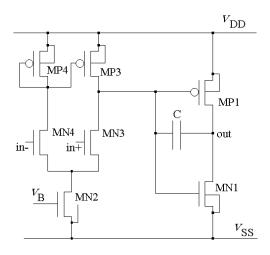

|   |                               | 4.2.1       | Operational amplifiers                                                        | 74   |  |  |

|   |                               | 4.2.2       | Capacitors and switches                                                       | 80   |  |  |

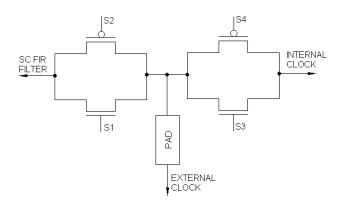

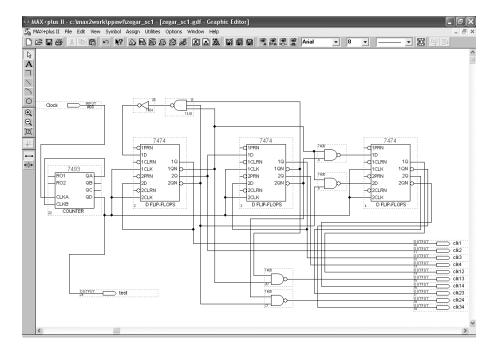

|   | 4.3                           | Contro      | ol clock systems                                                              | 81   |  |  |

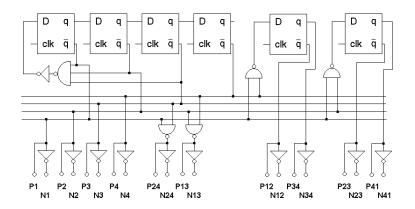

|   |                               | 4.3.1       | Internal clock systems                                                        | 82   |  |  |

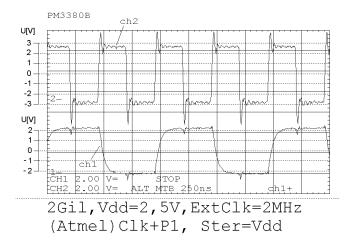

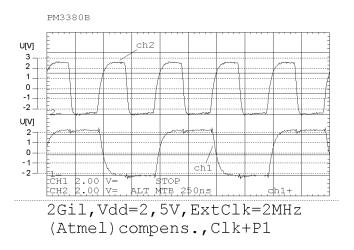

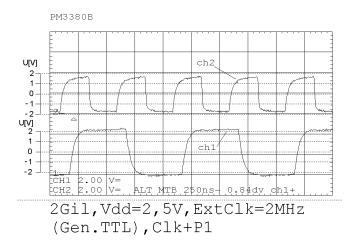

|   |                               | 4.3.2       | External clock systems                                                        | 88   |  |  |

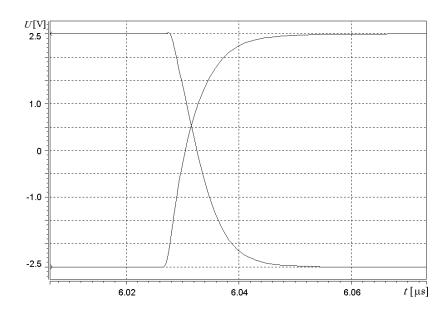

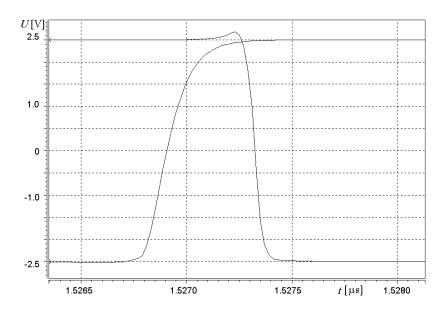

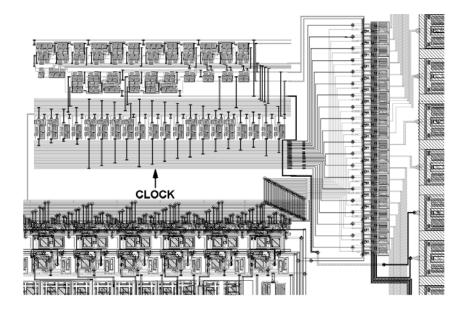

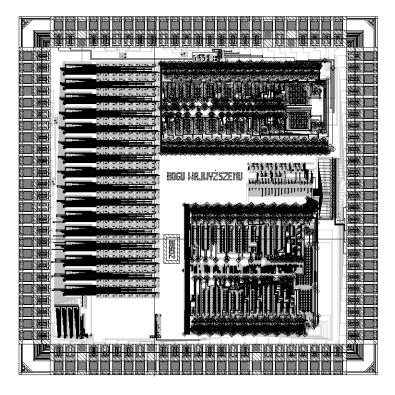

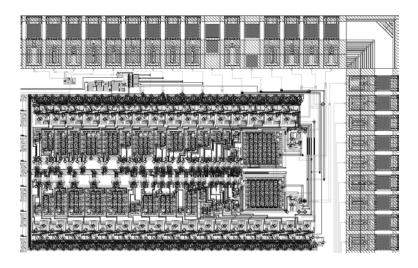

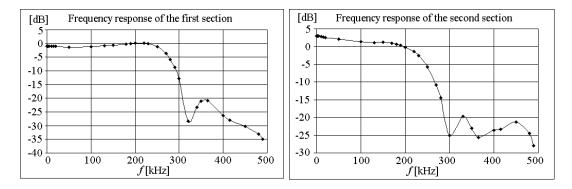

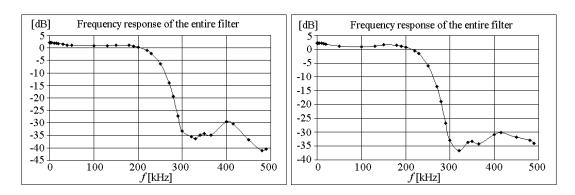

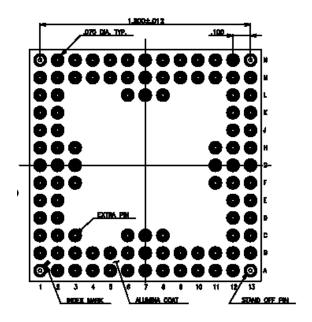

|   | 4.4                           | First p     | prototype of the GSM channel filter                                           | 92   |  |  |

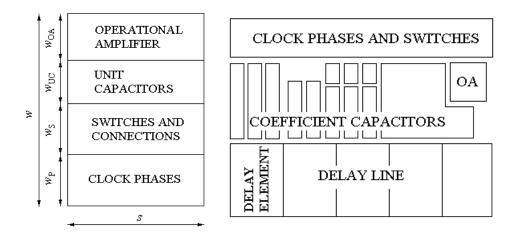

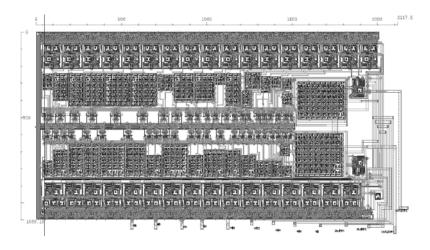

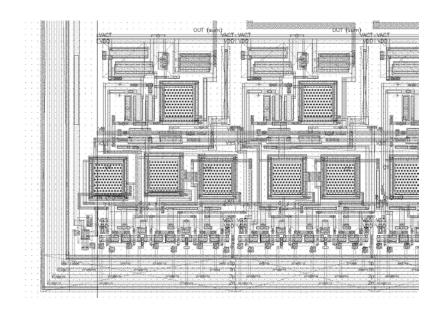

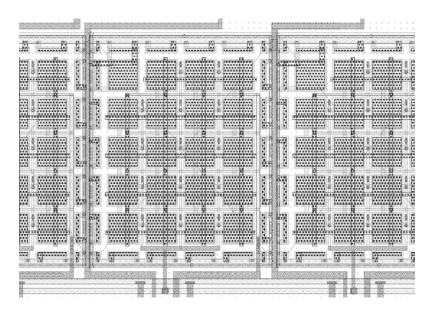

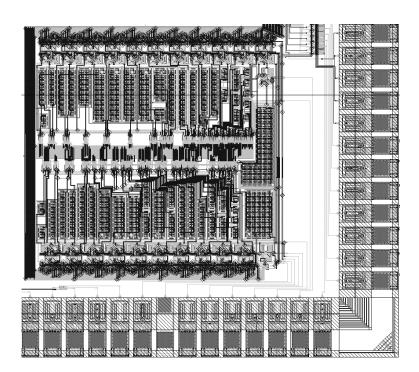

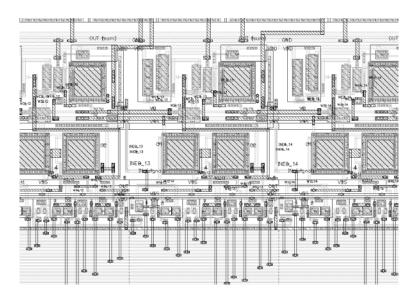

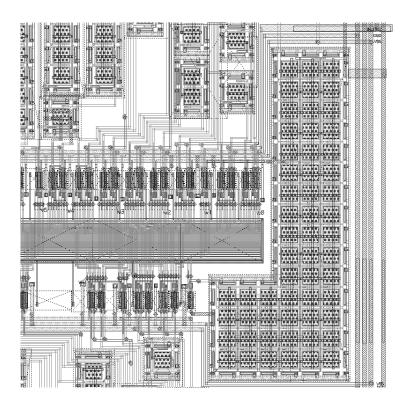

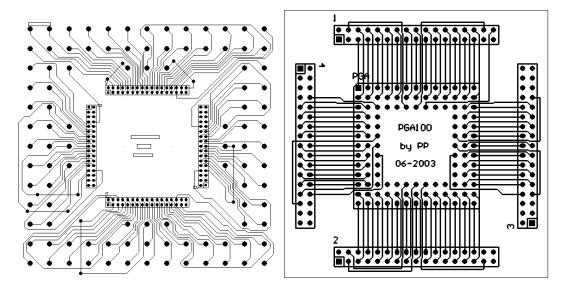

|   |                               | 4.4.1       | Design of filter layout                                                       | 92   |  |  |

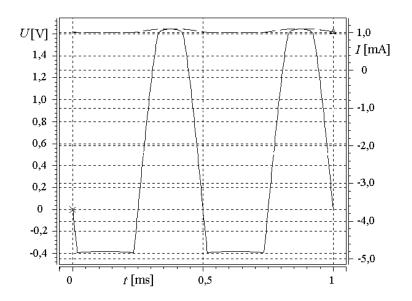

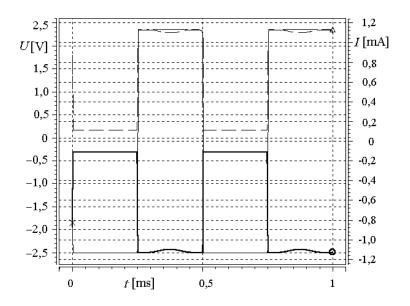

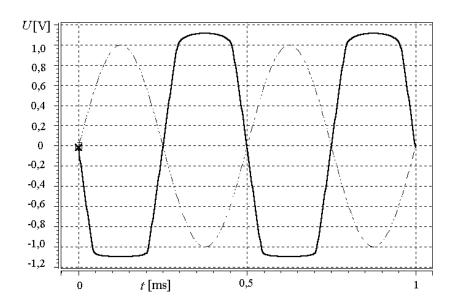

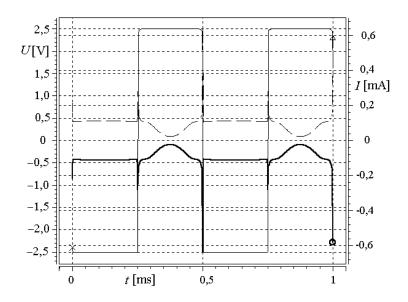

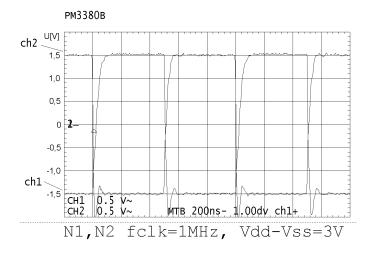

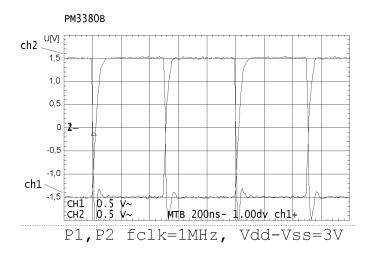

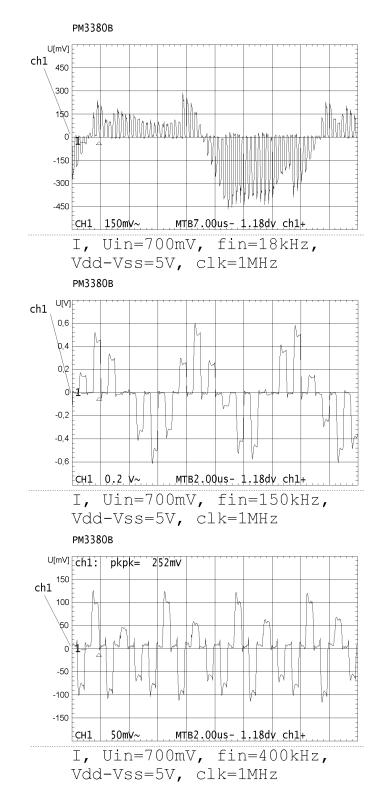

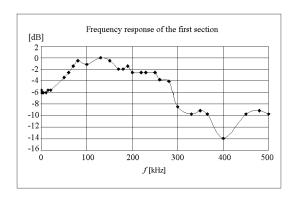

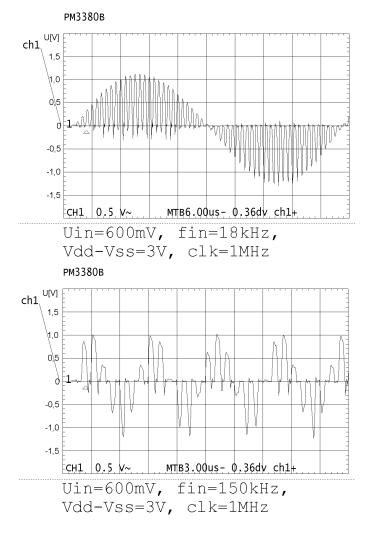

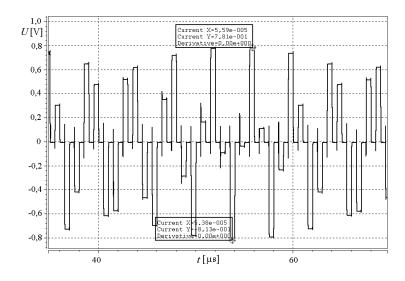

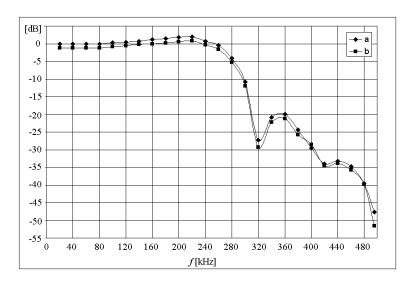

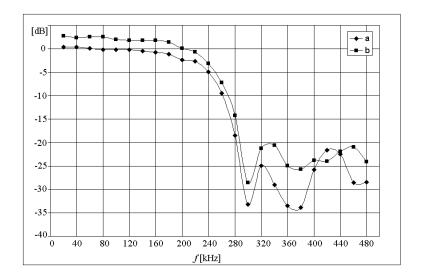

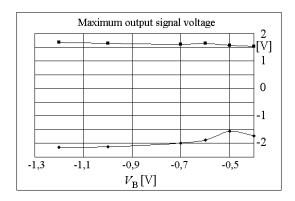

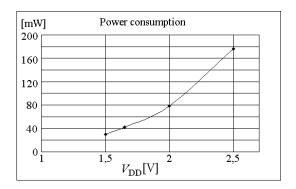

|   |                               | 4.4.2       | Chip measurements                                                             | 96   |  |  |

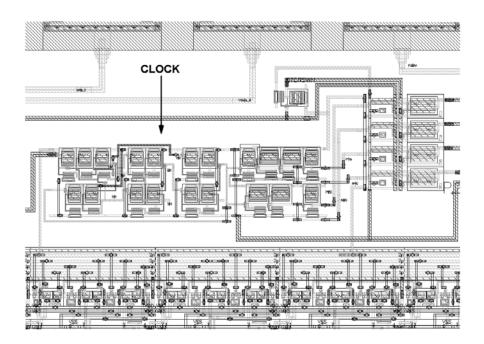

|   | 4.5                           | Second      | l prototype of the GSM channel filter                                         | 108  |  |  |

|   |                               | 4.5.1       | Design of the layout                                                          | 108  |  |  |

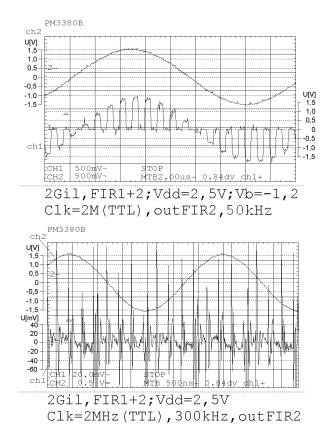

|   |                               | 4.5.2       | Measurements of the chip                                                      | 115  |  |  |

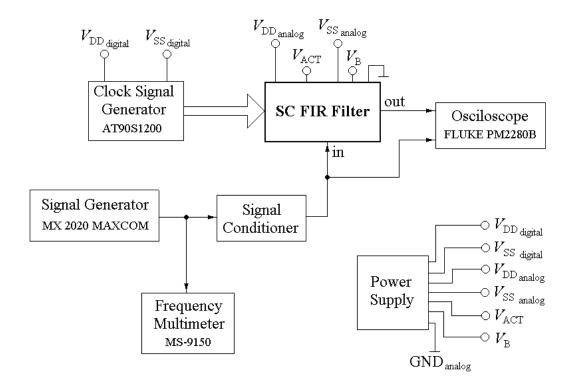

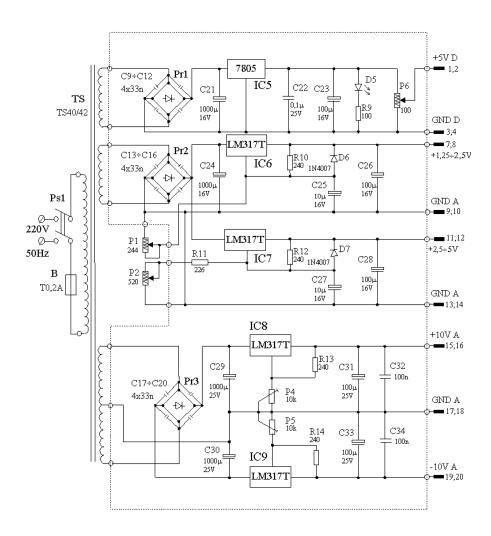

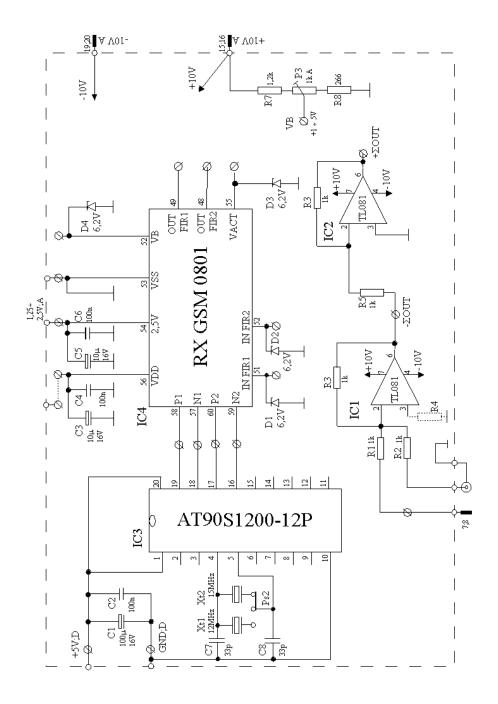

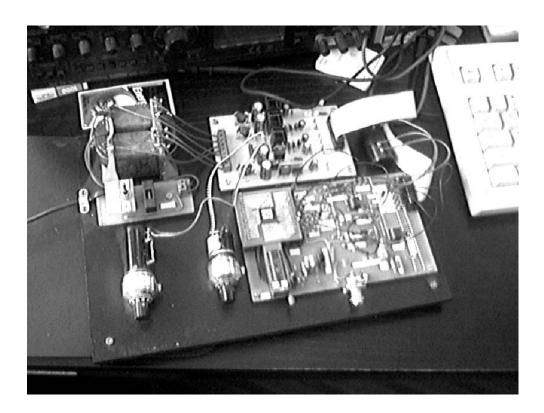

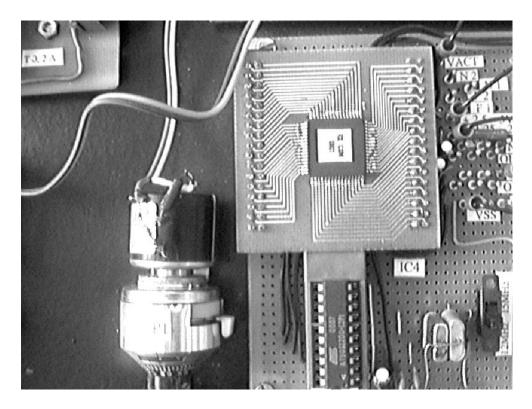

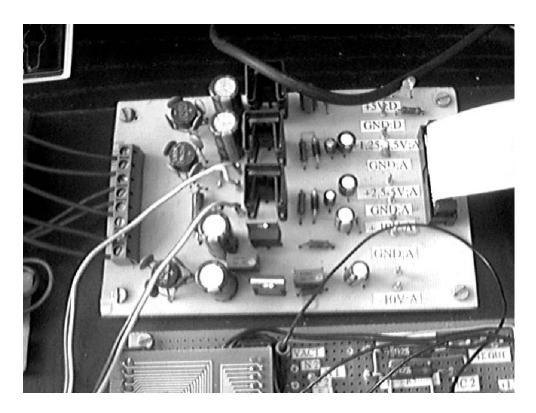

|   | 4.6                           | Measu       | rement environment                                                            | 125  |  |  |

| 5 | Con                           | Conclusions |                                                                               |      |  |  |

|   | Bib                           | liograp     | ohy                                                                           | 136  |  |  |

|   | List of author's publications |             |                                                                               |      |  |  |

# List of symbols and abbreviations

```

A — open loop gain of the operational amplifier

ASIC — application specific integrated circuit

CC — coefficient capacitor

C_{\rm C} — number of combinations of clock phases in the multi-C structure

div — natural division without rest

DSP — digital signal processor

f_{\rm clk} — frequency of the clock signal

f_{\rm in} — frequency of the input signal

FIR — finite impulse response

I_{\rm DD} — drain supply current

I_{\rm SS} — source supply current

L_{\rm CC} — number of coefficient capacitors

L_{hCC} — number of capacitors in the filter coefficient h_i in the multi-C structure

L_{h\text{CM}} — number of minimal capacitors with area S_{\text{CM}}

L_{\rm OA} — number of operational amplifiers

L_{\rm S} — number of switches

L_{\rm UC} — number of unit capacitors

mod — rest obtained from the natural division

MOS — metal-oxide-semiconductor

OA — operational amplifier

N — order of the finite impulse response filter

P — number of clock phases

P_{\rm CC} — chip area of the coefficient capacitors

P_{\text{DEL}} — chip area of the delay line

P_{\text{OAW}} — chip area of the output operational amplifier

P_{\rm SP} — chip area of the switches and clock pathes in the summer circuit

R — order of the "even" and "odd" delay elements

RISC — reduced instruction set computer

round — rounding of a real number

S — switch

S_{\rm C} — chip area of a single connection

S_{\rm CC} — chip area of a single coefficient capacitor

S_{\rm CM} — chip area of the minimal capacitor in the filter coefficient h_i

S_{\rm CT} — chip area of capacitors in all filter coefficients

S_{\rm OA} — chip area of a single operational amplifier

S_{\rm S} — chip area of a single switch

```

$S_{\mathrm{UC}}$  — chip area of a single unit capacitor

S(N) — total chip area

SC - switched capacitor

$\mbox{S\&H}$  — sample & hold delay element

SNR — signal-to-noise ratio

$U_{\text{off}}$  — offset voltage UC — unit capacitor

$V_{

m ACT}$  — activation on/off voltage

$V_{\rm B}$  — bias voltage

$V_{

m DD}$  — drain supply voltage

$V_{

m SS}$  — source supply voltage

VLSI — very large scale of integration

# Chapter 1

### Introduction

#### 1.1 Research area

Revolution in the monolithic integration of electronic filters began in the seventies with achievements in MOS VLSI (metal-oxide-semiconductor very large scale of integration) technology.

On the one hand, the ease of integrating perfect switches, precise capacitors (or more rigorously – precise capacitance ratios) and satisfactorily good operational amplifiers (OA's) led to an entirely new class of analog circuits, namely, to the switched-capacitor circuits (or SC circuits for short), i.e., circuits containing switches, capacitors, and active elements (e.g., OA's) [1].

On the other hand, however, digital single-chip integrated filters were developed concurrently to SC filters and the milestone on this way were general-purpose digital signal processors (DSP's) [4].

Construction of first SC filters was based on replacement of resistors present in classical active-RC filters by configurations of switches and capacitors. Direct approach to the design of SC filters is, however, also possible and in fact very promising. In this thesis the direct approach is considered and developed to the design and optimization of a very important class of filters, namely the FIR (finite impulse response) filters.

SC techniques have a lot of important advantages. The most important of them are: low power consumption for applications with low dynamic range, simple structure (low production costs) and a large degree of parallelism in the realization of certain signal processing tasks [1]. Thus, SC circuits can be preferable even for processing of signals at relatively high frequencies (in the range of MHz for modern sub-micron CMOS technology).

In SC techniques, the filter length is, in general, independent of the maximum frequency but is limited by the maximum chip area and by the minimum signal-to-noise ratio (SNR) [1, 2]. The chip area depends on the technology (among the currently used technologies are:  $0.35 \mu m$ ,  $0.8 \mu m$ , and sometimes still  $2 \mu m$  or  $3 \mu m$  CMOS).

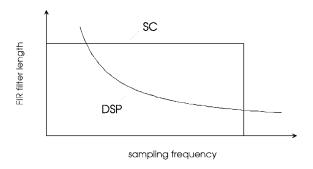

Figure 1.1: Performance limits for SC and DSP techniques [1]

It has to be stressed that around the seventies, digital systems started to replace analog solutions in almost all signal processing applications [6, 7, 31, 32]. One might even think that the era of classical frequency-domain signal processing, i.e., of high-precision analog filters, would have come to the limit, perhaps even to the end. This statement is, however, obviously not true. The need for constant miniaturization of electronic filters and the prolonged battery life (e.g., in portable units such as mobile phones) makes low-power and low-voltage design criteria more and more important for both analog and digital integrated circuits and in many situations favors analog (e.g., SC) solutions. Smaller dimensions and higher densities reduce the isolation barriers to a few volts and the power preventing chips from overheating to some milliwatts. For certain applications (in particular for the low-power and low-voltage case) switched-capacitor circuits have distinct advantages over their all-digital counterparts. The most important among them are:

- lower power consumption by about two orders of magnitude for applications in which a low dynamic range can be tolerated,

- simpler structure, resulting in lower design and production costs,

- larger degree of parallelism in the realization of certain signal processing algorithms.

From above properties it results that SC circuits, compared to digital realizations based on currently available DSP's [4, 49, 53], can be preferable for processing of signals at relatively high frequencies (i.e., in the range of several hundred kilohertz) as is illustrated in Fig. 1.1.

For a switched-capacitor realization, the filter length is limited by the maximum chip area and by the minimum signal-to-noise ratio (SNR) requirements. The upper limit for the sampling frequency, i.e., for the frequency range, is determined for SC filters by the bandwidth of OA's and by the maximum value of  $\tau \approx RC$ , where R is the onresistance of the switches and C is the maximum effective capacity in the circuit, which, in turn, is governed by the used technology. Owing to a CMOS process, frequencies of several hundred kilohertz can be achieved using clock rates of up to several megahertz.

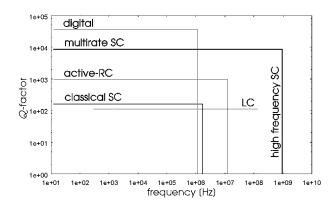

Figure 1.2: Transfer function Q-factor and frequency range limits for SC, digital, active-RC and LC filters [1]

For higher frequencies a faster process should be used, e.g., with a gallium arsenide (GaAs) technology.

For DSP realizations the maximum signal frequency depends on the operation cycle duration. For FIR filters of very small length, this maximum frequency limit is, as a rule, higher than that for an SC counterpart. Unfortunately, the required filter lengths are usually too large to be able to utilize this advantage. Thus, for most applications (those requiring large filter lengths) the resulting achievable sampling rate of a single DSP realization is relatively low. Accordingly, for typical sampling rates below, say 1 MHz, and filter lengths of the order of 50, the limits of realizability clearly favor SC implementations, as is confirmed in Fig. 1.1.

An important filter performance criterion is the attainable transfer function Q-factor, which is measure of the filter selectivity, i.e., the reverse of the relative passband width. The approximate performance capabilities, which can be achieved for the most important filter types are illustrated in 1.2.

The vertical axis shows the attainable Q-factor and the horizontal axis - the achievable operating frequency range. Typical SC filters are characterized by Q-factors limited to about 100 due to the limit on the maximum capacity ratio (the maximum capacitance is limited by the maximum realizable chip and the minimum capacitance by the technological tolerance and the requirements for the minimum SNR). Attainable Q-factor can, however, be extended to some thousands using multirate techniques. On the other hand, the frequency range limit of several hundreds of kilohertz can be extended to about 100 MHz by replacing CMOS technology by GaAs technology and also by the use of fast-settling OA's.

For comparison, classical LC filters can attain Q-factors of about 100 and the frequency range of the order of 100 MHz; but below say 1 kHz they become bulky and cumbersome. Active-RC filters can be designed for Q-factors up to about 1000 and for frequencies to around 10 MHz. Digital filters can achieve quite high Q-factors but they can operate up to only about 1 MHz with a single DSP realizations.

As we can see, particularly for low-power, low-voltage and/or low-dynamic range applications, as well as, for high Q values and high-frequency applications including multirate systems and filter banks, SC realizations can be clearly preferable to other analog approaches and to all-digital approaches. Moreover, SC circuits will dominate in implementation of the interface circuitry on the border between digital and analog systems. That is why considerations contained in this thesis are concentrated on SC realizations.

#### 1.2 Aim and scientific thesis

Scientific aim of this Ph. D. dissertation is the development of the design and optimization methods for electronic switched-capacitor (SC) finite impulse response (FIR) filters for their integration in the contemporary CMOS technologies [1, 9, 20]. This is a specific but in fact the most important class of analog integrated FIR filters.

Scientific thesis can be formulated as follows: the proposed, designed, and optimized SC FIR filter structures, realized in contemporary sub-micron CMOS technologies, are suitable for high frequencies and dynamic ranges. Thus, their application in modern communication and multimedia systems is not only possible but also favorable in relation to the application of all-digital solutions.

To prove this thesis a representative illustrative example has been chosen, namely the channel filter for the GSM (global system for mobile telephony) system. Various versions of such a filter have been designed, integrated, realized, and measured.

The considered (existing and proposed new) SC FIR filter structures have been evaluated from the perspective of the efficiency of their integration and the perfection of their operation. The proposed evaluation process, used in this dissertation, is comprised of various criteria such as the chip area, clock system complexity, power consumption, and the output signal quality. Three following evaluation stages have been distinguished.

The first stage is a very quick, rough, and efficient theoretical comparison of SC FIR architectures, which uses only a general knowledge of the number of various elements. In this stage the design of the whole integrated circuit is not necessary, which is obviously a very important advantage of this approach. The most important advantage consists in the fact that the evaluation results obtainable using this method occurred to be very plausible.

For instance already at this stage it was possible to prove that filters with a relatively large spread of coefficients, typical for higher order selective filters, are not realizable as SC circuits, opposed to their all-digital counterparts. In a digital case large spread of coefficients is usually only a problem of secondary importance. This is, however, not the case for SC filters, because a very large chip area would be required to realize them. That is why an optimization method has been proposed, which consists in a division of an original, i.e., single, and usually quite long filter into a cascade of shorter sections. It has been shown that after the proposed optimization the spread of coefficients in

each of such sections is substantially lower. This considerably reduces the required chip area – typically even by many orders of magnitude.

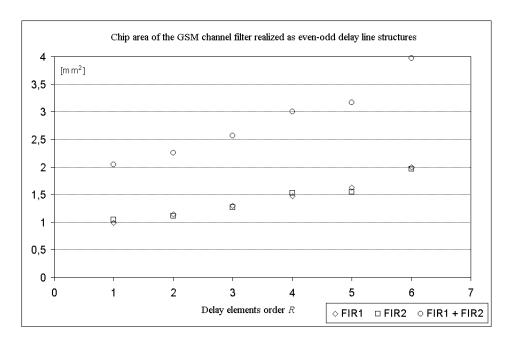

Already at this stage it was also possible to evaluate many SC FIR filter families, among them a new family based on the so-called even-odd delay line structures [1]. Furthermore, introduction of the higher order even-odd delay line structures allows for improvement of many parameters.

The second evaluation stage is certainly the design and optimization of the whole integrated circuit in a prescribed technology and its verification by a large number of simulations. This is a necessary but very arduous stage.

The third and last stage is certainly the chip fabrication and then its measurement. Selected SC FIR filters have been fabricated and successfully verified.

The proposed three stage design and optimization process has proved to be very effective and efficient. Experiences gained at the first stage have been very useful at the second stage and finally resulted in successful chips with optimized parameters.

# Chapter 2

# General characteristic of switched capacitor circuits

#### 2.1 Basics of the SC technique

In the seventies of the 20th century there began a revolution in the integration of electronic filters with important achievements in MOS VLSI technology. It became possible to integrate perfect switches, precise capacitors (with respect to capacitance ratios), and good operational amplifiers (OA's) [60, 61, 62]. This led to entirely new class of analog circuits - the switched-capacitor (SC) circuits [1, 9, 11]. The main idea of this kind of circuits lies in the possibility of replacing resistors with configurations of switches and capacitors. Combinations of switches and capacitors simulate resistors. The basic theoretical considerations presented in this Chapter are based on the book [1] written by the promoter of this thesis.

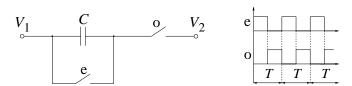

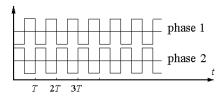

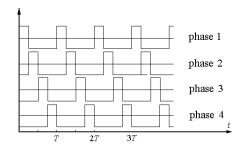

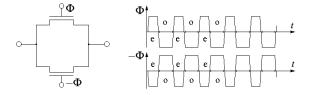

An illustrative circuit and the clock control with two clock phases ("e" and "o") is presented in Figure 2.1. T is the time period of the clock.

Figure 2.1: SC realization of a resistor and clock control

In the time period  $\Delta t = T$  the charge, which flows trough the capacitor is given by equation (2.1). In practice, this charge can be interpreted as a  $\Delta q$  in the time period T.

$$q = U \cdot C = (V_1(t_n) - V_2(t_n)) \cdot C.$$

(2.1)

Current in the capacitor is given by equation (2.2)

$$i_{\rm C}(t_n) = \frac{\Delta q}{\Delta t} = \frac{U \cdot C}{T} \,.$$

(2.2)

If we replace capacitor and switches by the resistor with resistance R, current will be the same as in equation (2.3)

$$i_{\mathcal{R}}(t_n) = \frac{U}{R} \,. \tag{2.3}$$

Thus we can write

$$I_{\rm C} = I_{\rm R} \text{ for } R = \frac{T}{C}.$$

(2.4)

Above equations show that SC filters are the discrete-time circuits, with the analog representation of the voltage signal. Such circuits can be easily realized in different CMOS technologies, because they do not need resistors. This feature is important as CMOS technologies, which are relatively cheap, do not contain high-resistive layers, and as a result the integration of resistors is a difficult task. In the BiCMOS technologies the high-resistive layers are present, but these technologies are much more expensive than the CMOS.

#### 2.2 Building blocks of the SC FIR filters

SC FIR filters contain only three basic elements, such as: switches (S's), unit (UC's) and coefficient (CC's) capacitors and operational amplifiers (OA's). These elements are parts of the basic building blocks such as the memory elements and summer circuits. Many different SC memory elements have been proposed in literature [3, 10, 21, 22, 23, 24, 25, 26, 27, 28, 29]. Summer circuits [2, 30] in SC technique join two different functions: multiplication and addition of the signal samples. Illustrative memory elements and summer circuits are shortly described below.

#### 2.2.1 SC memory elements

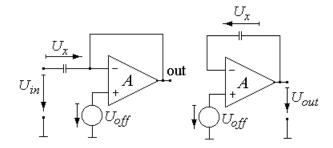

#### Sample & hold delay element

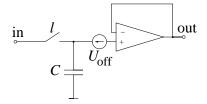

This element (see Figure 2.2) stores the signal sample in the capacitor. The OA works in the follower configuration and the output of the OA is equal to the value of the signal sample. The sample can by read many times, what is an advantage of this kind of circuits. Signal sample is stored in the l phase and can be read in the any phase m. Output voltage as a function of the input voltage is given by equation (2.5)

$$u_{\text{out}}(m) = \frac{1}{1 + 1/A} (u_{\text{in}}(l) + u_{\text{off}}) \approx u_{\text{in}}(l) + u_{\text{off}}.$$

(2.5)

Figure 2.2: Sample & hold memory element

where A is an open loop gain of the OA,  $u_{\text{off}}$  is the OA offset voltage.

#### Nagaraj memory element

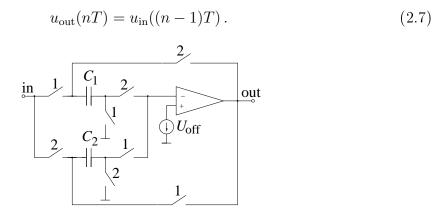

Figure 2.3 illustrates the delay element proposed by Nagaray [25]. This element is driven by a two phase clock, what is advantageous. Analysis of this circuit leads to equation (2.6)

$$(C_1 + \frac{C_1 + C_{s1} + C_s}{A}) \cdot u_{\text{out}}(nT) =$$

$$C_1 u_{\text{in}}((n-1)T) + \frac{C_s}{A} u_{\text{out}}((n-1)T) + (C_1 + C_{s1}) u_{\text{off}}.$$

(2.6)

Disadvantage of this memory element is the fact that the output voltage depends on the offset voltage of the OA. Assuming  $A \to \infty$  and  $U_{\text{off}} \to 0$  equation (2.6) reduces to equation (2.7)

Figure 2.3: Nagaray memory element

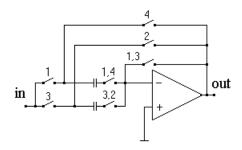

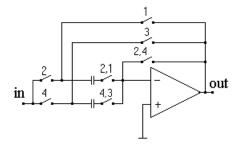

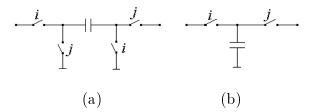

#### Gilligham delay element

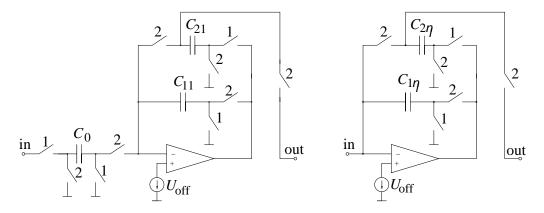

In Figure 2.4 two versions of the Gillingham delay element are presented. First block (a) is used at the beginning of the delay line and the second block (b) is used for all

Figure 2.4: Gillingham delay elements: (a) used at the beginning of the delay line (b) used for all other delay elements

other delay elements in the delay line. The Gillingham delay element is driven by a two phase clock, which is advantageous. For these elements we can write the equations (2.8) and (2.9)

$$u_1((n+1)T) = \frac{C_0}{C_{11}}u_{\rm in}(nT) + u_{\rm off1},$$

(2.8)

and

$$u_1((n+2)T) = \frac{C_{11}}{C_{21}}u_1((n+1)T) + u_{\text{off1}} - u_{\text{off2}}.$$

(2.9)

Notice that for the block (b) we have

$$u_{\rm in\eta}(nT) = u_{\rm off\eta} \,. \tag{2.10}$$

Thus we obtain

$$u_{\eta}((n+2\eta-1)T) = \frac{C_{2(\eta-1)}}{C_{1\eta}} u_{\eta-1}([n+2(\eta-1)]T) - u_{\text{off}(\eta-1)} + u_{\text{off}\eta}, \qquad (2.11)$$

and finally

$$u_{\eta}((n+2\eta)T) = \frac{C_{1\eta}}{C_{2\eta}}u_{\eta}((n+2\eta-1)T) - u_{\text{off}\eta} + u_{\text{off}(\eta+1)}.$$

(2.12)

Assuming, that all capacitors have the same capacities, we can write

$$u_{\eta}((n+2\eta-1)T) = u_{\rm in}(nT) + u_{\rm off1},$$

(2.13)

and

$$u_n((n+2\eta)T) = u_{\text{in}}(nT) + u_{\text{off}1} + u_{\text{off}\eta} - u_{\text{off}(\eta+1)}. \tag{2.14}$$

These equations show, that this element is sensitive to the offset voltage of a practically single OA, however, this is due to sensitivity to capacitor mismatch.

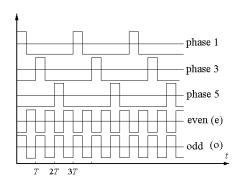

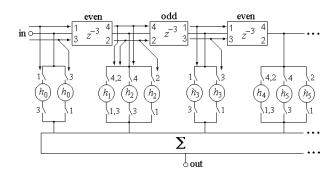

#### Even and odd delay elements

Dąbrowski, Menzi, and Moschytz proposed in 1989 the delay elements, which are offset voltage compensated and are insensitive to the capacitor mismatch. There exist two basic versions of them: even and odd delay element, which should be connected alternately in the delay line. Analysis of these elements is presented in Section 3.6.

#### 2.2.2 SC summer circuits

#### Lee-Martin summer

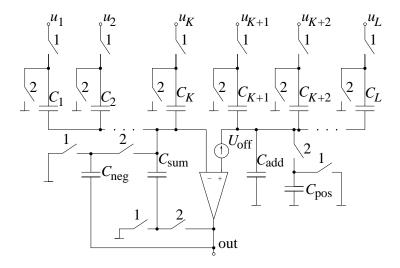

Figure 2.5: Lee-Martin summer

The output voltage as a function of the input voltages is given by equation (2.15)

$$u_{\text{out}}(nT) = -\sum_{i=1}^{K} \frac{C_i}{C_{\text{sum}}} u_i(nT) + \sum_{i=K+1}^{L} \frac{C_i}{C_{\text{sum}}} u_i(nT).$$

(2.15)

under convenient assumption that  $C_{\text{sum}} + \sum_{i=1}^{K} C_i = C_{\text{add}} + \sum_{i=K+1}^{L} C_i$ . This circuit is offset voltage compensated in the first clock phase.

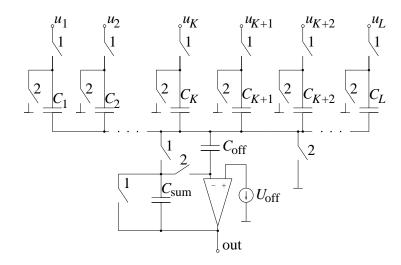

Figure 2.6: Recharge summer

The output voltage as a function of the input voltages is given by equation (2.16)

$$u_{\text{out}}(nT) = -\sum_{i=1}^{K} \frac{C_i}{C_{\text{sum}}} u_i((n-1)T) + \sum_{i=K+1}^{L} \frac{C_i}{C_{\text{sum}}} u_i((n-1)T).$$

(2.16)

#### 2.3 Theoretical SC FIR filter architectures

The family of the SC FIR filters contains different architectures, presented briefly in this subsection. These structures posses both advantages and disadvantages. In practice it is necessary to seek the compromise between these features for each particular application.

There exist basic SC FIR filter structures and composite structures, which are compositions of the basic structures.

#### 2.3.1 Basic SC FIR filter structures

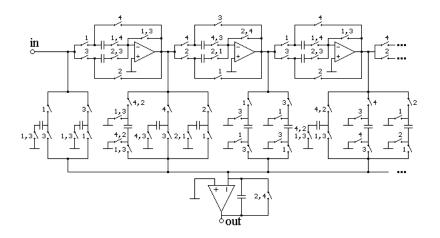

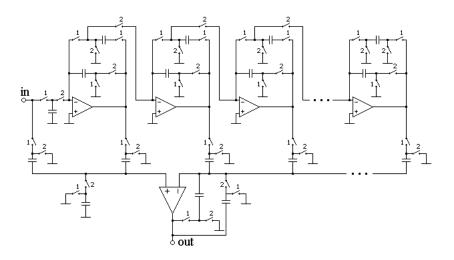

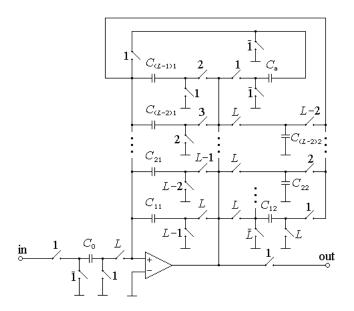

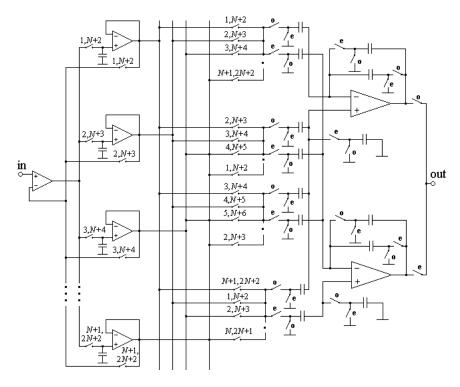

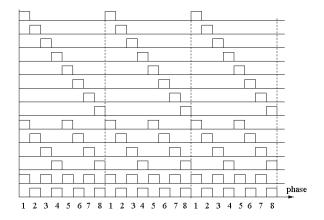

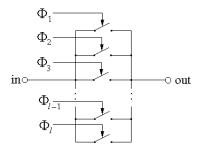

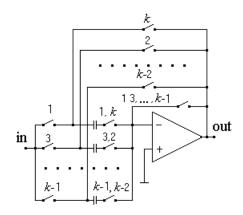

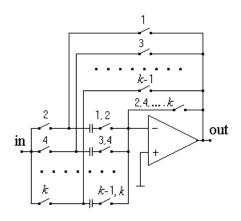

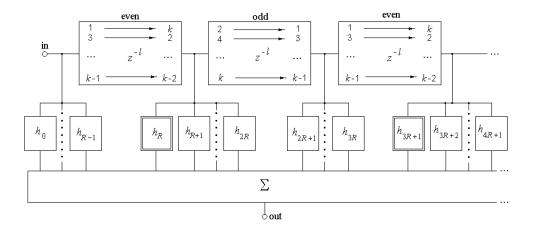

• Delay line structures: These architectures are either a tapped delay line structure or as a reversed delay line structure. Both of them can be realized in parallel ("data read" and "data write" operations are performed in the same phases in all delay elements) or serially (i.e., one after the other, thus composing a single filter operation cycle). In the first case, a great number of OA's, and a small number of clock phases are necessary. Structures of this kind can be based either on even-odd delay elements [1, 3] (structure No. 1, see Figure 2.7) or on Gillingham delay element (structures No. 2 and 3, see Figures 2.8 and 2.9). Advantages and

disadvantages of each of these structures result, in particular, from properties of the even-odd (see Section 3.6) and the Gillingham delay elements. Among advantages of the even-odd delay elements are: compensation of the offset-voltage and insensitivity to the capacitor mismatch. The last property results from the fact that  $U_{\rm out}$  in the even and odd delay elements are independent of the values of capacitors. Structure No. 1 is driven by a four phase clock but with only two clock phases per sample. On the other hand, the Gillingham element requires only a two phase clock. The disadvantage of structures No. 2 and No. 3 is their sensitivity to capacitor mismatch and to offset-voltage. Nevertheless, the offset errors do not accumulate along the delay line, what is obviously an important advantage.

In the case of serial realizations, a single OA suffices but a complex multiphase clock is required (delay line structures No. 4 and 5, see Figures 2.10 and 2.11). Structure No. 5 realizes a reversed delay line.

The main disadvantage of all delay line structures is their sensitivity to overwrite errors accumulated along the line during the "data read" and "data write" operations.

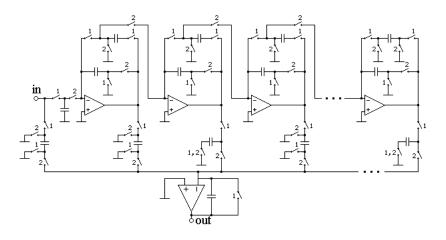

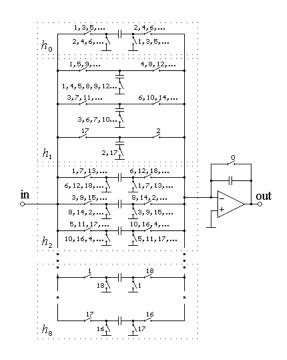

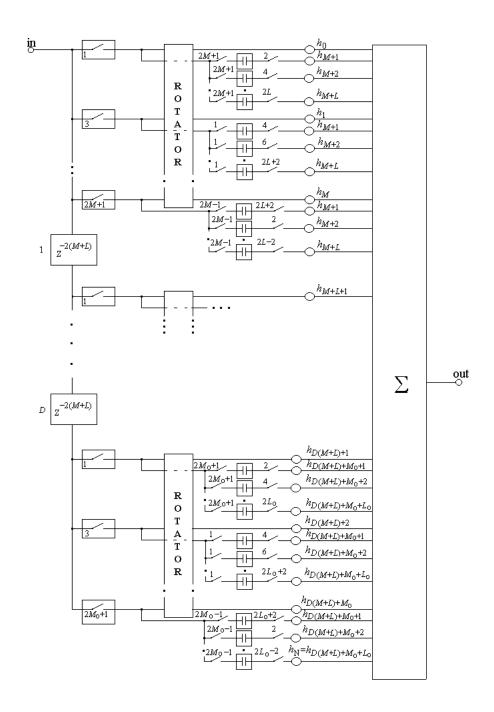

- Rotator FIR structure: This structure comprises the so-called rotator switch that connects signal samples with capacitors of the summer circuit (see Figures 2.13, 2.14 and 2.15). The signal samples are stored in sample-and-hold delay elements. Structures of this kind are characterized by large numbers of OA's and many switching phases, but the clock system is a simple structure and particular switches are driven by only one clock phase. In these structures the upper frequency range does not depend on the filter order N, because only two clock phases occur during processing of one of the signal samples.

- Parallel or multi-C FIR structure: In this structure, signal samples are stored in individual capacitors. The advantages are: no cumulative errors (in opposition to the delay line structures) and a single active element only (see Figure 2.12). The disadvantages are: a great number of switching phases: 2(N+1), where N is the filter order, and a very large number of capacitors, i.e., about  $(N+1)^2$ . In this structure numerous switches are driven by more than one clock phase and this fact creates an additional problem, which concerns the separation of the clock phases.

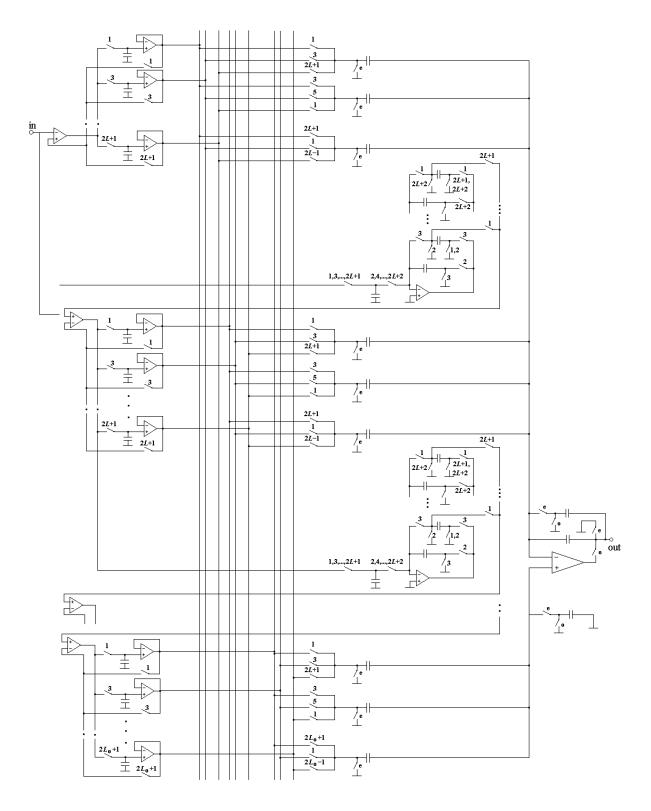

#### 2.3.2 Composite SC FIR filter structures

The disadvantages of particular basic structures become a problem when the filter order N is high. In such cases it is necessary to look for new solutions, which minimize disadvantages of basic structures. The problem can be solved to a certain degree by introducing a family of composite structures, i.e., those, which are composed of at least two basic structures. Composite structures allow realizing compromise solutions, in which disadvantages are reduced to substructures and in result are masked

by advantages of other substructures. However, composite structures are usually more complicated and thus more difficult in the CMOS realization.

Derivation of different composite SC FIR filter structures is based on the so-called "morphological approach" [17]. In this method we look for all realizable composite SC FIR filter structures. The morphological approach adapted to the design of composite SC FIR filters consists of the following five steps:

- 1. Problem formulation: We are going to realize composite SC FIR filter configurations using the basic SC FIR filter structures. Then we shall qualify them according to the following criteria: number of circuit elements, chip area, operation speed, network performance, clock complexity, etc.

- 2. Characterization of fundamental elements: The following four basic SC FIR structures serve as the fundamental elements for the so-called "morphological box": multi-op-amp delay line FIR structure, multiphase delay line FIR structure, parallel (multi-C) FIR structure, rotator FIR structure.

- 3. Derivation of a morphological box: In the case under discussion this is a multi-dimensional box with four basic structures (those listed above) placed along each dimension. The possible solutions correspond to different positions in the box. Theoretically we could consider composite structures containing an arbitrary number of stages realized with basic structures but practically we shall limit ourselves to two or at most three of them.

- 4. Evaluation of solutions contained in the morphological box: Many of the theoretically possible solutions are not realizable or unreasonable in practice. Thus we eliminate them using the following rules:

- In order to reduce the number of OA's, the parallel (multi-C) FIR structure should be applied as the last link of a composite filter structure or followed by a delay line with recharge branches and recharge summer circuits. Signal samples (charges on capacitors) can be read only once.

- A particular basic structure can (in practice) occur only once in a composite structure. Two consecutive identical basic structures can be combined into one. Configurations composed of more than two basic structures are of little practical concern.

- Structures equivalent to a tapped delay line are suitable for the first link, while structures realizing the reversed delay line are well fitted for the last link.

Taking the above conditions into account, we obtain 8 reasonable composite FIR SC configurations, which are presented in the next subsection.

5. Evaluation of the solutions: A selection of superior solutions among the FIR SC structures obtained in step 4 can be based on the evaluation of their feasibility as integrated circuits and on their performance in applications.

####

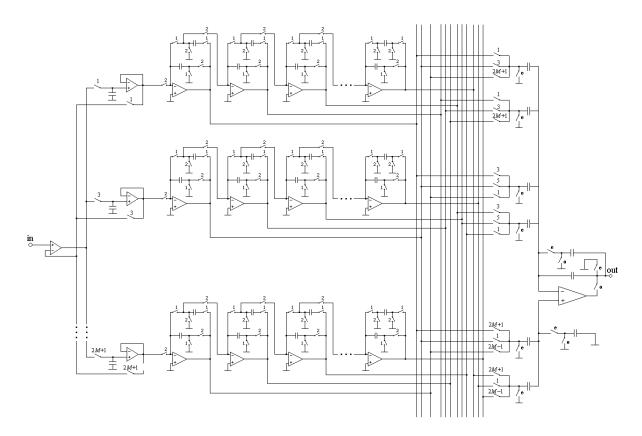

Figure 2.7: Delay line structure No. 1

Figure 2.8: Delay line structure No. 2

Figure 2.9: Delay line structure No. 3

Figure 2.10: Delay line structure No. 4

Figure 2.11: Delay line structure No. 5

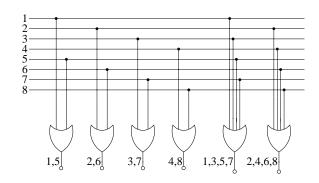

Figure 2.12: Multi-C structure for N=8

Figure 2.13: Rotator structure No. 1

Figure 2.14: Rotator structure No. 2

Figure 2.15: Rotator structure No. 3

Figure 2.16: Delay line - multi-C structure

Figure 2.17: Delay line - rotator structure  $\,$

Figure 2.18: Delay line - rotator - multi-C structure

Figure 2.19: Rotator - multi-C structure

Figure 2.20: Rotator - delay line structure

Figure 2.21: Fischer structure

# Chapter 3

# Comparison and evaluation of the SC FIR filter structures

In this Chapter the methods for comparing and evaluating the SC FIR filters are presented. One of the most important parameters is the chip area of the integrated circuit. This parameter exerts a great influence on the total cost of the integrated circuit.

The evaluation of the chip area on the basis of some theoretical assumptions presented in the next Subsection [33, 36], is a very simple and efficient method as it does not require the whole design process. It is, however, only a rough evaluation, although in most cases it offers plausible results.

The weakest assumption of the simplified approach are constant values of particular filter elements resulting in reservation of the constant chip areas for them. In reality the filter element values strongly depend on the filter frequency response. Thus estimation of the plausible substitute (averaged) element values is a very important task for this evaluation method.

In order to improve the exactness of the results of the simplified approach the author modified and improved it by taking actual element values into account [34, 48]. Using this new approach it was possible to show that for many practical filter frequency responses the required chip area is unrealistic large, if they are to be realized directly (like digital filters). In order to overcome this severe problem the author suggested a method for optimization (minimization) of the chip area. It is based on the following principle: a single high order (i.e. long) filter should be split into some shorter sections connected in a cascade.

The chip area evaluation method and the method for the minimization of the chip area are presented in the third Subsection of this Chapter. This method was used to compute optimum values of coefficients for filters realized as integrated circuits. They are presented in the fourth Chapter of this dissertation.

In the third Subsection of this Chapter we present a problem of realization of clock systems for SC FIR filters [38, 43, 49]. Particular SC FIR filter structures are driven

Figure 3.1: Theoretical organization of the chip area

by clock systems with different degrees of complexity. The clock systems effect many other parameters of the integrated circuit also the chip area. In this Subsection we also propose and compare different solutions for the clock systems.

In the next two Sections we compare SC FIR filters from the perspective of the power consumption and the quality of the signal processing.

Comparison of filters on the basis of all these different criteria led the author to postulating a new family of the even-odd delay line structures [46]. The even-odd delay line structures introduced earlier [1, 3] are in this thesis called the first order structures. The author postulates a family of higher order even-odd delay elements and consequently — higher order delay line structures. The resulting filters are presented and evaluated in the last Subsection of this Chapter.

# 3.1 Evaluation of the chip area on the basis of theoretical assumptions

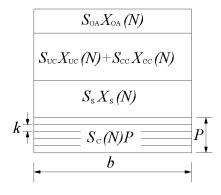

#### 3.1.1 Chip area estimation

To estimate the required chip area for a particular FIR structure, it is necessary to determine the number of the elements as a function of the filter order N [33, 36]. Then we consider the equation (3.1)

$$S(N) = S_{\text{OA}}L_{\text{OA}}(N) + S_{\text{UC}}L_{\text{UC}}(N) + S_{\text{CC}}L_{\text{CC}}(N) + S_{\text{S}}L_{\text{S}}(N) + S_{\text{C}}(N)P, \quad (3.1)$$

where:

S(N) - the entire chip area, N - filter order,  $S_{\rm C}$  - area of a single connection, P - number of clock phases,  $S_{\rm OA}$  - area of a single OA,  $L_{\rm OA}(N)$  - number of OA's,  $S_{\rm UC}$  - area of a single unit capacitor (UC),  $L_{\rm UC}(N)$  - number of UC's,

$S_{\text{CC}}$  - area of a single coefficient capacitor (CC),  $L_{\text{CC}}(N)$  - number of CC's,  $S_{\text{S}}$  - area of a single switch (S),  $L_{\text{S}}(N)$  - number of S's.

Assuming that the chip shape is approximately square (see Fig. 3.1), we can write

$$S_{\rm C} = k\sqrt{S_{\rm OA}L_{\rm OA} + S_{\rm UC}L_{\rm UC} + S_{\rm CC}L_{\rm CC} + S_{\rm S}L_{\rm S}} = kb.$$

(3.2)

Coefficient  $S_{\rm C}$  results from the necessity of assigning some part of the chip area for connections. This area depends linearly on the number of clock phases P. Coefficient k depends on the technology used, b is the length of the chip equal to the square root of the area of all filter elements. Coefficients  $S_{\rm OA}$ ,  $S_{\rm UC}$ ,  $S_{\rm CC}$ ,  $S_{\rm S}$  depend also on the technology. We use their estimated values. The values for parameters  $L_{\rm OA}$ ,  $L_{\rm UC}$ ,  $L_{\rm CC}$ ,  $L_{\rm S}$ , i.e., numbers of particular elements, are computed in the next Subsection individually for all considered structures.

#### 3.1.2 Number of elements as a function of the filter order N

Equations given in tables below comprise the following denotations:

- div the natural division without rest,

- mod rest obtained from the natural division,

- round rounding of a real number, in the used interpretation, e.g., round(2.50) = 2 but round(2.51) = 3 (for the purpose used in this Subsection rounding of numbers with more than two fractional digits is not necessary).

Table 3.1: Number of elements used in the delay line structure No. 1

|                   | Delay line                       | Summer                       | Total                                                                                                              |

|-------------------|----------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------|

| $L_{\mathrm{OA}}$ | $N - (N+1) \operatorname{div} 3$ | 1                            | N+1- $(N+1)  div  3$                                                                                               |

| $L_{ m S}$        | 7N - 7[(N+1)  div  3]            | 6N + 7 - 3[(N+2)  div  3]    | $   \begin{array}{c}     13N + 7 - \\     7[(N+1) \text{ div } 3] - \\     3[(N+2) \text{ div } 3]   \end{array} $ |

| $L_{\rm UC}$      | 2[N - (N+1)  div  3]             | 0                            | 2[N - (N+1)  div  3]                                                                                               |

| $L_{\rm CC}$      | 0                                | 2 + 2N + 1 - [(N+2)  div  3] | $3 + 2N - [(N+2) \operatorname{div} 3]$                                                                            |

| P                 | 4                                | 4                            | 4                                                                                                                  |

Table 3.2: Number of elements used in the delay line structure No. 2 and 3

|                   | Dela       | y line No. | 2      | Delay line No. 3 |        |        |

|-------------------|------------|------------|--------|------------------|--------|--------|

|                   | Delay line | Summer     | Total  | Delay line       | Summer | Total  |

| $L_{\mathrm{OA}}$ | N          | 1          | N+1    | N                | 1      | N+1    |

| $L_{ m S}$        | 6N + 1     | 2N + 8     | 8N + 9 | 6N + 1           | 3N + 7 | 9N + 8 |

| $L_{\rm UC}$      | 2N + 1     | 0          | 2N+1   | 2N + 1           | 1      | 2N+2   |

| $L_{\rm CC}$      | 0          | N+4        | N+4    | 0                | N+2    | N+2    |

| P                 | 2          | 2          | 2      | 2                | 2      | 2      |

Table 3.3: Number of elements used in the delay line structure No. 4 and 5

|                   | Delay line No. 4 | Delay line No. 5 |

|-------------------|------------------|------------------|

|                   | Total            | Total            |

| $L_{\mathrm{OA}}$ | 1                | 1                |

| $L_{\rm S}$       | 4N + 11          | 5N + 11          |

| $L_{\rm UC}$      | N+2              | N+2              |

| $L_{\rm CC}$      | N+1              | N+1              |

| P                 | 2(N+1)           | 2(N+1)           |

Table 3.4: Number of elements used in the delay line - multi-C structure

|                   | Delay line  | Multi-C - Summer | Total                      |

|-------------------|-------------|------------------|----------------------------|

| $L_{\mathrm{OA}}$ | D           | 1                | D+1                        |

| $L_{\rm S}$       | D[3+6(L+1)] | $3DC + 3C_0 + 1$ | $D(6L+9) + 3DC + 3C_0 + 1$ |

| $L_{\rm UC}$      | D[1+2(L+1)] | 0                | D(2L+3)                    |

| $L_{\rm CC}$      | 0           | $DC + C_0 + 1$   | $DC + C_0 + 1$             |

| P                 | 2(L+1)      | 2(L+1)           | 2(L+1)                     |

#### where:

N - filter order, L - order of a previous multi-C section,  $L_0$  - order of the last multi-C section, D - number of delay elements, and D=(N+1) div (L+1)-B. If  $(N+1) \mod (L+1)=0$  then B=1 else B=0;  $L_0=(N+1)-D(L+1)$ . Number of capacitors in previous sections is equal to  $C=\left[\frac{(L+2)(L+1)}{2}+\sum\limits_{i=1}^{L}(L+1) \mod (i+1)\right]$  and number of capacitors in the last section to  $C_0=\left[\frac{(L_0+2)(L_0+1)}{2}+\sum\limits_{i=1}^{L_0}(L_0+1) \mod (i+1)\right]$ .

Table 3.5: Number of elements used in the delay line - rotator structure

|                   | S&h       | Delay line      | Rotator              | Summer                                      | Total                                   |

|-------------------|-----------|-----------------|----------------------|---------------------------------------------|-----------------------------------------|

| $L_{\mathrm{OA}}$ | 1 + N + 1 | D               | 0                    | 1                                           | N+D+3                                   |

| $L_{ m S}$        | 2(N+1)    | $2D+ \\7D(L+1)$ | $D(L+1)^2 + (L+1)^2$ | $ \begin{array}{c c} N+\\ 1+6 \end{array} $ | $3(N+1) + 2D + D(L+1)(L+8) + (L_0+1)^2$ |

| $L_{ m UC}$       | N+1       | D+ 2D(L+1)      | 0                    | 0                                           | $N+1+ \\ D(2L+3)$                       |

| $L_{\rm CC}$      | 0         | 0               | 0                    | $N+ \\ 1+3$                                 | N+4                                     |

| P                 | 2(L+1)    | 2(L+1)          | 2(L+1)               | 2                                           | 2(L+1)                                  |

#### where:

N - filter order, L - rotator order,  $L_0$  - order of the last section, D - number of delay elements and D=(N+1) div (L+1)-B. If (N+1) mod (L+1)=0 then B=1 else B=0;  $L_0=(N+1)-D(L+1)$ .

Table 3.6: Number of elements used in the multi-C structure

| Table 3.6: Number of elements used in the multi-C structure |                                                                |        |                                                                   |  |

|-------------------------------------------------------------|----------------------------------------------------------------|--------|-------------------------------------------------------------------|--|

|                                                             | $\operatorname{Multi-C}$                                       | Summer | Total                                                             |  |

| $L_{\mathrm{OA}}$                                           | 0                                                              | 1      | 1                                                                 |  |

| $L_{ m S}$                                                  | $3\frac{N+2(N+1)}{2} + 3\sum_{i=1}^{N} (N+1) \mod (i+1)$       | 1      | $3\frac{N(N+2)(N+1)}{2} + 3\sum_{i+1}^{N} (N+1) \mod (i+1) + 1$   |  |

| $L_{\rm UC}$                                                | 0                                                              | 0      | 0                                                                 |  |

| $L_{\rm CC}$                                                | $\frac{\frac{(N+2)(N+1)}{2}}{\sum_{i=1}^{N} (N+1) \mod (i+1)}$ | 1      | $\frac{\frac{(N+2)(N+1)}{2}}{\sum_{i+1}^{N}(N+1) \mod (i+1) + 1}$ |  |

| P                                                           | 2                                                              |        | 2(N+1)                                                            |  |

Table 3.7: Number of elements used in the rotator structure No. 1

|                   | Sample & hold | Rotator   | Summer    | Total        |

|-------------------|---------------|-----------|-----------|--------------|

| $L_{\mathrm{OA}}$ | 1 + N + 1     | 0         | 1         | N+3          |

| $L_{ m S}$        | 2(N+1)        | $(N+1)^2$ | N + 1 + 6 | (N+1)(N+4)+6 |

| $L_{\mathrm{UC}}$ | N+1           | 0         | 0         | N+1          |

| $L_{\rm CC}$      | 0             | 0         | N + 1 + 3 | N+4          |

| P                 | 2(N+1)        | 2(N + 1)  | 9         | 2(N+2)       |

Table 3.8: Number of elements used in the rotator structure No. 2

|                   | Sample & hold                | Rotator   | Summer   | Total                      |  |

|-------------------|------------------------------|-----------|----------|----------------------------|--|

| $L_{\mathrm{OA}}$ | 1 + (N+1)                    | 0         | 2        | N+4                        |  |

| $L_{\rm S}$       | 2(N+1)                       | $(N+1)^2$ | 6(N+1)+4 | (N+1)(N+9)+4               |  |

| $L_{\rm UC}$      | N+1                          | 0         | 0        | N+1                        |  |

| $L_{\rm CC}$      | 0                            | 0         | 2(N+1)+2 | 2(N+1)+2                   |  |

| Р                 | $N_{\rm odd}$ $N_{\rm even}$ |           |          | $N_{ m odd}$ $N_{ m even}$ |  |

|                   | $N+1 \mid 2(N+1)$            |           |          | $N+1 \mid 2(N+1)$          |  |

Table 3.9: Number of elements used in the rotator structure No. 3

|                   | Sample & hold              | Rotator   | Summer    | Total                      |

|-------------------|----------------------------|-----------|-----------|----------------------------|

| $L_{\mathrm{OA}}$ | 1 + (N+1)                  | 0         | 2         | N+4                        |

| $L_{\mathrm{S}}$  | 2(N+1)                     | $(N+1)^2$ | 4(N+1)+14 | (N+1)(N+7)+14              |

| $L_{\rm UC}$      | N+1                        | 0         | 0         | N+1                        |

| $L_{\rm CC}$      | 0                          | 0         | 2(N+1)+6  | 2(N+1)+6                   |

| Р                 | $N_{ m odd}$ $N_{ m even}$ |           |           | $N_{ m odd}$ $N_{ m even}$ |

|                   | $N+1 \mid 2(N+1)$          |           |           | $N+1 \mid 2(N+1)$          |

Table 3.10: Number of elements used in the delay line - rotator - multi-C structure

|                   | Delay line                  | S&H                  | Rotator                | Multi-C                                                                                                           | Total                                                              |

|-------------------|-----------------------------|----------------------|------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| $L_{\mathrm{OA}}$ | D                           | $D(M+2)+ (M_0+2)$    | 0                      | 1                                                                                                                 | $D(M+3)+ (M_0+2)$                                                  |

| $L_{ m S}$        | 9 <i>D</i> +<br>7 <i>DF</i> | $2[D(M+1)+ (M_0+1)]$ | $D(M+1)^2 + (M_0+1)^2$ | $     \begin{array}{r}       1+\\       3[(1+L)\cdot\\ (M+1)D+\\ (M_0+1)\cdot\\ (1+L_0)]   \end{array} $          | $D(M+1) \cdot (M+3L+6) + (M_0+1) \cdot (M_0+3L_0+6) + D(7F+3) + 1$ |

| $L_{ m UC}$       | 3D+2DF                      | $D(M+1)+ (M_0+1)$    | 0                      | 0                                                                                                                 | $D(4+2F+M)+ M_0+1$                                                 |

| $L_{ m CC}$       | 0                           | 0                    | 0                      | $   \begin{array}{c}     1+ \\     D(M+1) \cdot \\     (1+L)+ \\     (M_0+1) \cdot \\     (1+L_0)   \end{array} $ | $D(M+1) \cdot (1+L) + (M_0+1) \cdot (1+L_0) + 1$                   |

| P                 |                             |                      |                        |                                                                                                                   | 2(M+1)                                                             |

#### where:

M - rotator order; L - number of capacitors in a single multi-C section; F - order of previous sections of the rotator - multi-C type;  $M_0$  - the last rotator order;  $L_0$  - number of capacitors in the last multi-C section;  $F_0$  - the last section rotator - multi-C order; D - number of delay elements; N - filter order; and D=(N+1) div (F+1)-B; If (N+1) mod (F+1)=0 then B=1 else B=0;  $F_0=(N+1)-D(F+1)$ ;  $M_{\min}=$  round (F/2+0.01);  $M_{0\min}=$  round (F/2+0.01); L=F-M;  $L_0=F_0-M_0$ .

Table 3.11: Number of elements used in the rotator - delay line structure

|                   | S&H       | Delay line  | Rotator        | Summer  | Total         |

|-------------------|-----------|-------------|----------------|---------|---------------|

| $L_{\mathrm{OA}}$ | 1 + (M+1) | (M+1)L      | 0              | 1       | (M+1)(L+1)+2  |

| $L_{ m S}$        | 2(M+1)    | (M+1)(1+6L) | $(M+L+1)\cdot$ |         |               |

|                   |           |             | (M + 1)        | 1 + 6   | (M+1)(7L+M+5) |

| $L_{\rm UC}$      | M+1       | 2L(M+1)     | 0              | 0       | (M+1)(2L+1)   |

| I aa              | 0         | 0           | 0              | M + L + | M+L+4         |

| $L_{\rm CC}$      | U         | U           | U              | 1 + 3   | M + L + 4     |

| P                 | 2(M+1)    | 2           | 2(M+1)         | 2       | 2(M+1)        |

#### where:

M - rotator order, L - order of a single delay line, N=M+L.

Table 3.12: Number of elements used in the rotator - multi-C structure

|                   | S&H       | Rotator   | MultiC  | Summer                                       | Total        |

|-------------------|-----------|-----------|---------|----------------------------------------------|--------------|

| $L_{\mathrm{OA}}$ | 1 + M + 1 | 0         | 0       | 1                                            | M+3          |

| $L_{ m S}$        | 2(M+1)    | $(M+1)^2$ | 3L(M+1) | $ \begin{array}{c} 1+\\ 3(M+1) \end{array} $ |              |

| $L_{\rm UC}$      | M+1       | 0         | 0       | 0                                            | M+1          |

| $L_{\rm CC}$      | 0         | 0         | L(M+1)  | 1+ (M+1)                                     | (M+1)(L+1)+1 |

| P                 | 2(M+1)    | 2(M+1)    | 2L      | 2                                            | 2(M+1)       |

#### where:

N - filter order, M - rotator order, L - number of capacitors in a single multi-C section and  $M_{\min} = \text{round } (N/2 + 0.01), L = N - M$ .

Table 3.13: Number of elements used in the Fischer structure

|                   | previous sections | last section    | Total             |

|-------------------|-------------------|-----------------|-------------------|

| $L_{\mathrm{OA}}$ | D                 | 1               | D+1               |

| $L_{\mathrm{S}}$  | D(30+3)           | $4(L_0+1)+6$    | $33D + 4L_0 + 10$ |

| $L_{\rm UC}$      | 8D                | $1 + (L_0 + 1)$ | $8D + L_0 + 2$    |

| $L_{\rm CC}$      | 7D                | $L_0 + 1$       | $7D + L_0 + 1$    |

| P                 | 8                 | $L_0$           | 8                 |

#### where:

N - filter order, D - number of previous sections,  $L_0$  - last section order and D=N+6-B. If N div 6=0 then B=1 else B=0;  $L_0=N-6D$ ,  $L_0<6$ .

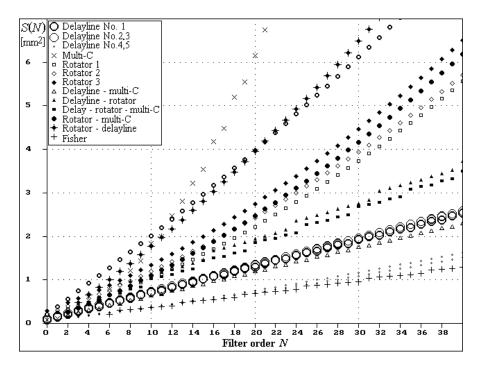

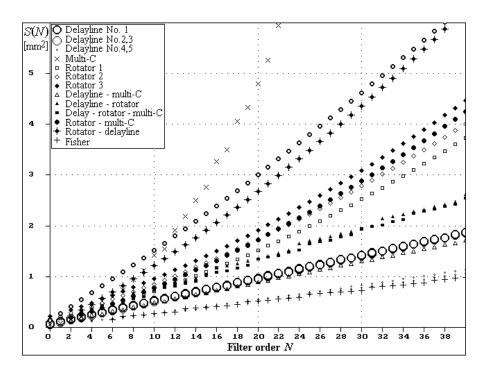

Figure 3.2: Chip areas for 3  $\mu$ m CMOS technology

#### 3.1.3 Conclusions

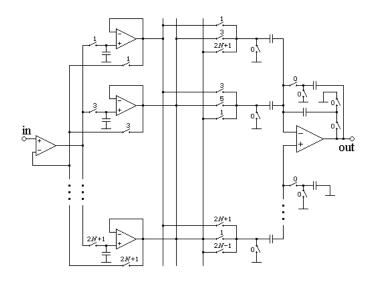

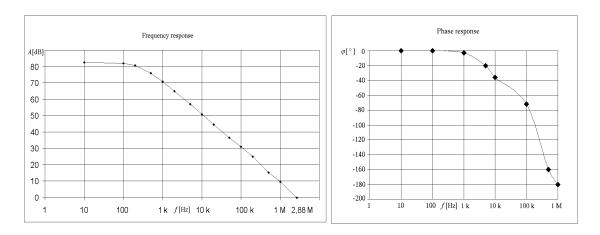

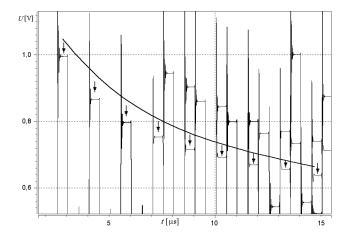

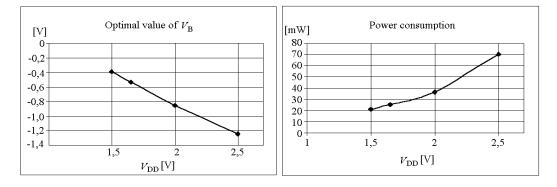

The estimated chip areas are presented in Figures 3.2, 3.3, 3.4, as functions of the filter order N for 3  $\mu$ m, 2  $\mu$ m and 0.8  $\mu$ m CMOS technologies, respectively, and for SC FIR filter structures described in the second Chapter of this dissertation.

If we improve the technology, the area of particular elements will decrease but not linearly along with the technology parameters. In consequence, the entire chip area will decrease. The greatest area change can be noted for OA's (3.7 : 1 for the change from 3  $\mu$ m to 0.8  $\mu$ m CMOS technology). Intermediate changes

can be observed for switches (3.33:1). The change of the area of capacitors is smaller, i.e., about 1.8:1. In consequence the highest progress appears in these structures, which comprise larger numbers of OA's (rotator, delay lines No. 1, No. 2, No. 3) and smaller numbers of capacitors. Thus some structures, which from the perspective of chip area are preferable in one technology, are not such in the other technology. For example, the chip area of a multi-C structure (N=20) is equal to 6.2 mm<sup>2</sup> for 3  $\mu$ m CMOS technology but 2.9 mm<sup>2</sup> for 0.8  $\mu$ m CMOS technology. It means that the chip area can be decreased by 2.1:1. For the rotator structure this ratio is greater. It equals 3.2:1. The rotator structure comprises a large number of OA's and, therefore, the improvement is bigger than in the case of the multi-C structure, which comprises a large number of capacitors but only a single OA.

A vast scope of freedom exists as far as the design of composite structures is concerned. A filter of order N can be realized in many different ways, e.g., the order of the rotator-delay line structure is given by N = M + L. One of the values M and L can be treated

Figure 3.3: Chip areas for 2  $\mu$ m CMOS technology

Figure 3.4: Chip areas for 0.8  $\mu$ m CMOS technology

as a parameter. The chip area will in every case be different. To evaluate the optimal chip area, function S = f(M, L) must be calculated to find the best partition of N to M and L.

### 3.2 Evaluation of the chip area on the basis of the real values of SC FIR filter coefficients

In this Section we present an improved method of evaluating the chip area. The method presented in the last subsection has an important disadvantage, which is the constant value of the area of the coefficient capacitors. In practice the chip area of these elements depends on the frequency response of the filter. When the spread of the values of the filter coefficient is high, then the total area of all coefficient capacitors is also very high. In the next part we present two extreme cases of the frequency responses. One is the filter with all equal coefficient values, and the second is the Butterworth (flat) filter with big dispersion of the values of the filter coefficients. When the filter order N is high and, additionally, the dispersion between coefficients is high (like in the Butterworth filter), then the total chip area of the filter is very high. In results such filters as whole are not realizable in the SC technique.

Because of this, a new method based on the filter decomposition into sections was proposed to solve this problem. It is presented in the following Subsection. At the end the obtained results are presented.

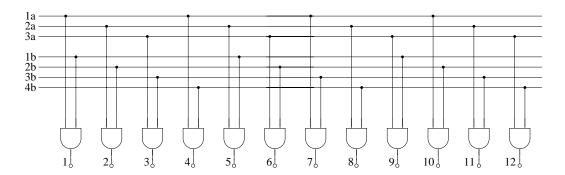

### 3.2.1 Influence of the frequency response of the filter on the chip area

In the SC FIR filters, coefficients are realized as ratios of capacitors in the input branches of the summer circuit (the coefficient capacitors) to the capacitor in the feedback of the operational amplifier at the output of the summer circuit. These coefficient capacitors (CC's) are built with tiny unit capacitors (UC's) connected in parallel. In practice, the coefficient with the smallest value is represented by a single UC. Other coefficients contain more than one UC, proportionally to their values. In the case of a high spread of the filter coefficients, the largest CC needs a lot of UC's and, in consequence, the total number of UC's (and the whole chip area) is high.

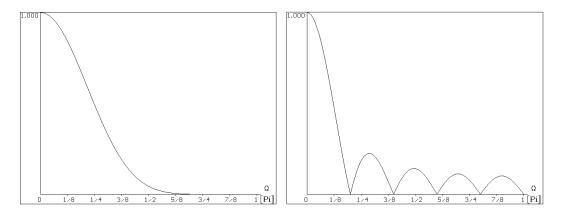

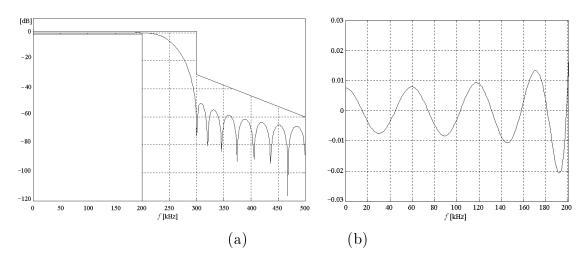

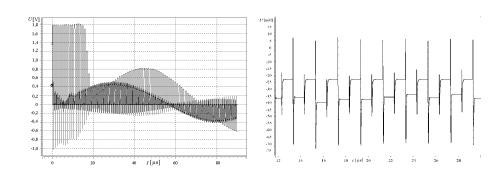

Figure 3.5 shows frequency responses of two illustrative low-pass filters. The first one (Fig. 3.5a) is the Butterworth filter and the second one (Fig. 3.5b) is the DFT-type filter. In the first case, the coefficients of the filter of order N are determined by the N'th row in the Pascal triangle (Fig. 3.6) in such a way that each coefficient (corresponding to a particular position in this row) is divided by the sum of all coefficients in this row. Thus, the greater the filter order N, the greater is the coefficient spread. In the second case no spread occurs because all coefficients are equal. For instance, for

Figure 3.5: Frequency responses of the illustrative low-pass filters: (a) Butterworth (flat) filter (N = 9), (b) DFT-type filter (all coefficients  $h_i$  are equal) (N = 9)

| N=1 | 1 1                 |

|-----|---------------------|

| N=2 | 1 2 1               |

| N=3 | 1 3 3 1             |

| N=4 | 1 4 6 4 1           |

| N=5 | 1 5 10 10 5 1       |

| N=6 | 1 6 15 20 15 6 1    |

| N=7 | 1 7 21 35 35 21 7 1 |

Figure 3.6: The Pascal triangle

the Butterworth filter of order N=9 we need the coefficients

$$\{h_i\} =$$

$\{0.00195; 0.01758; 0.07031; 0.16406; 0.24609; 0.24609; 0.16406; 0.07031; 0.01758; 0.00195\} \ .$

These values are characterized by a quite large spread of about 128.

It can be shown that the total area of capacitors  $S_{\rm CT}(N)$  required for the integration of the Butterworth filter of order N, if realized directly using the delay-line structure No. 2 or No. 3, is given by the following equation

$$S_{\rm CT}(N) = \frac{2}{h_{i\min}} S_{\rm CM} = 2^{N+1} S_{\rm CM},$$

(3.3)

where: N – filter order,  $h_{i\min}$  – the minimal coefficient  $h_i$ ,  $S_{\rm CM}$  - area of the minimal capacitor (it should be a multiple of the unit capacitor area  $S_{\rm UC}$ ). Assume, for example, that  $S_{\rm CM}=3800~\mu{\rm m}^2$  then for N=40 we would get  $S_{\rm CT}\approx8400~{\rm m}^2$ , which is obviously an absurd result.

In the multi-C structure (Fig. 2.12) each signal sample is stored in an individual capacitor. Because of this each coefficient  $h_i$  is composed of several capacitors and

therefore the number of capacitors increases very fast with the filter order N. This results from the fact that the number of coefficient capacitors (CC's) in each coefficient  $h_i$  is equal to at least i and is given by the following formula

$$L_{hCC}(i, N) = i + 1 + (N+1) \mod (i+1),$$

(3.4)

where: N – filter order, i = 0, ..., N, and "mod" means the remainder in the natural division.

The total number of capacitors in the multi-C structure is given by the equation

$$L_{\rm CC} = \frac{(N+2)(N+1)}{2} + \sum_{i=0}^{N} (N+1) \mod(i+1).$$

(3.5)

In the multi-C structure there is a single OA ( $L_{\rm OA}=1$ ), about  $3L_{\rm CC}$  S's ( $L_{\rm S}=3L_{\rm CC}$ ), and  $L_{\rm UC}=0$ .

For the Butterworth filter realized with the multi-C structure the appropriate equation for the total area of capacitors  $(S_{\text{CT}}(N))$  is as follows

$$S_{\rm CT}(N) = \sum_{i=0}^{N} (L_{hCC}(i, N) + 1) L_{hCM}(i, N) S_{\rm CM}, \qquad (3.6)$$

where:  $L_{hCC}(i, N)$  is given by equation (3.4),  $L_{hCM}(i, N)$  is the number of minimal capacitors with area  $S_{CM}$  in each of the CC's in a particular coefficient  $h_i$ .  $L_{hCM}(i, N)$  can be computed by the recursive formula

$$L_{hCM}(i, N) = 1$$

for  $i = 0$  and arbitrary  $N$ ;

$$L_{hCM}(i, N) = L_{hCM}(i - 1, N - 1) + L_{hCM}(i, N - 1)$$

for  $0 < i < N$ . (3.7)

The additional term +1 in the Equation (3.6) results from the fact that the feedback capacitor has the same area as the sum of all capacitors in coefficients  $h_i$ .

The second case (Fig.3.5b) is the DFT-type filter, i.e., that, whose all coefficients are equal. It is obviously the most convenient case for the realization as an integrated circuit. For instance, in the case of N=9,  $h_i=0.1$ ,  $i=0,1,\ldots,9$ . In result, the total capacitor area  $S_{\rm CT}(N)$  rises linearly with the filter order N according to the equation (3.8) valid for the delay-line structures No. 2, and No. 3 and according to the equation (3.9) for the multi-C structure.

$$S_{\rm CT}(N) = 2(N+1)S_{\rm CM},$$

(3.8)

$$S_{\rm CT}(N) = 2\sum_{i=0}^{N} (L_{hCC}(i, N) + 1)S_{\rm CM}.$$

(3.9)

Equation (3.9) is a special case of equation (3.6) with  $L_{h\text{CM}}(i, N) = 1$  for all i and N. It is worth noting that from equation (3.6) we can obtain the same result as from equation (3.3) if  $L_{h\text{CC}}(i, N) = 1$  for all i and N (for the delay line structures No. 2 and No. 3).

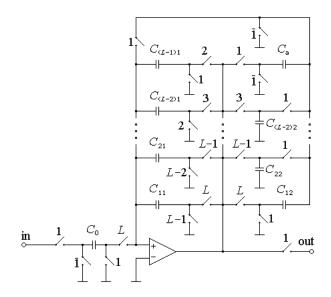

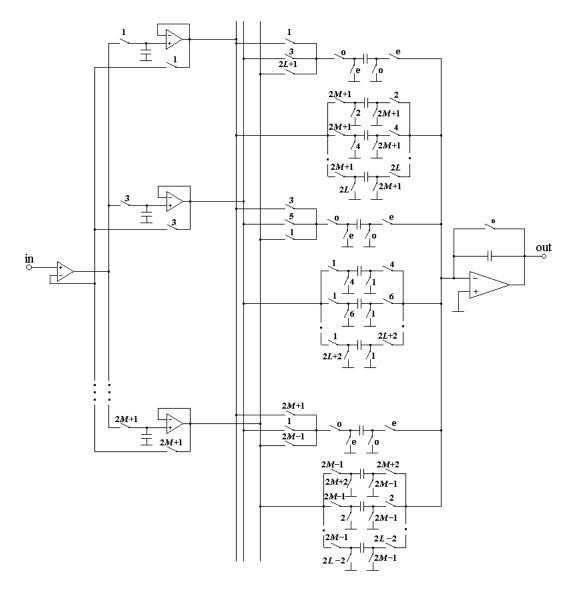

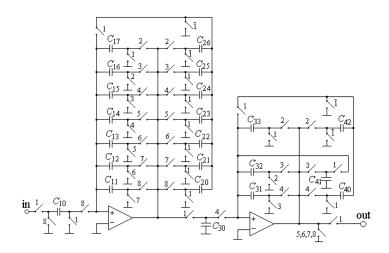

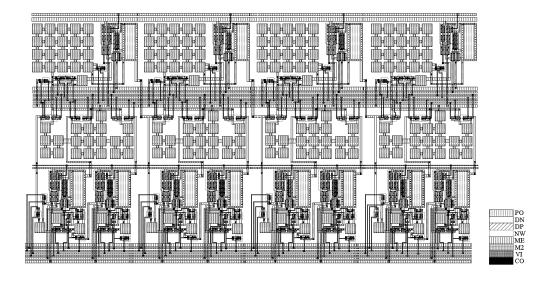

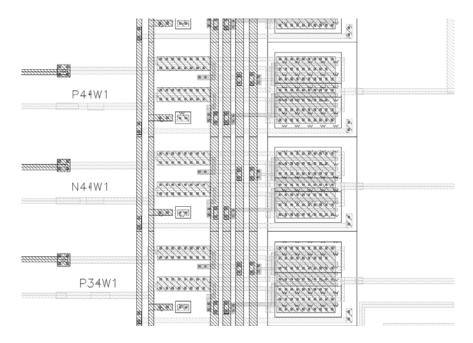

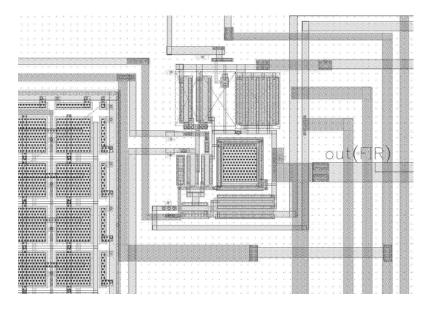

Figure 3.7: Layout of the section with the delay-line structure No. 3 (N=2)

The above considerations and examples show that the integration of an SC FIR filter, whose transfer function is directly (i.e., as a whole) realized, has a limited range of use. We propose two different approaches to overcome this serious difficulty:

- a cascade decomposition of the whole filter transfer function into sections of the second order (and possibly into a single first order section if the filter order is odd),

- a polyphase decomposition of the transfer function and the use of the composite structures [1, 33].

Figure 3.8: Layout of the composite (cascade) delay-line structure No. 3 (N=8)

Both solutions are characterized by many additional advantages. Among the most important are:

- modular structure,

- reduced number of clock phases (in some cases only),

- simpler layout and the reduced chip area,

- increased frequency range,

- lower sensitivity.

The cascade decomposition significantly simplifies the realization of the FIR Butterworth filters, because in this case we can use identical second order sections with coefficients  $\{h_i\} = \{0.25; 0.5; 0.25\}$  (Fig.3.7) and possibly a single first order section with coefficients  $\{h_i\} = \{0.5; 0.5\}$ . As an example, the cascade realization of the FIR Butterworth filter of order 8 is shown in 3.8. The circuits shown in Figs.3.7 and 3.8 have the following dimensions:  $980 \times 420 \, [\lambda]$  and  $980 \times 1750 \, [\lambda]$ , respectively,  $(1 \, \lambda = 0.6 \, \mu \text{m})$  for  $1.2 \, \mu \text{m}$  CMOS technology).

Cascaded delay-line structures possess important advantages:

- a simple two-phase (or four-phase) clock,

- possibility for partial outputs after each section,

- high modularity.

There are, however, also some disadvantages:

- larger number of active and other elements,

- accumulation of the rewrite errors,

- additional delay of  $z^{-0.5}$  per section (if the recharge summers are used).

Delays introduced by the second order sections comprising the recharge summers give rise to a need for two types of such sections: the even and the odd section. Sections of these two types have to be interleaved in the filter structure. The presence of the additional delay makes it difficult to use these sections in adaptive systems, as in such case no displacement between the plant output and the adaptive filter output is allowed.

For FIR Butterworth filters the total area of capacitors in summers of all sections can be determined by the following formula

$$S_{\rm CT}(N) = 8S_{\rm CM}(N \, \text{div} \, 2) + 4S_{\rm CM}(N \, \text{mod} \, 2),$$

(3.10)

where: "div" means the natural division without rest. The number of Gillingham delay elements in the cascade realization does not change in comparison to the direct realization and equals N-1. The number of OA's in the summer circuits is, however, higher and equals

$$L_{\text{OA}}(N) = N \operatorname{div} 2 + b, \qquad (3.11)$$

where

$$b = \begin{cases} 1 & \text{for odd } N \\ 0 & \text{for even } N. \end{cases}$$

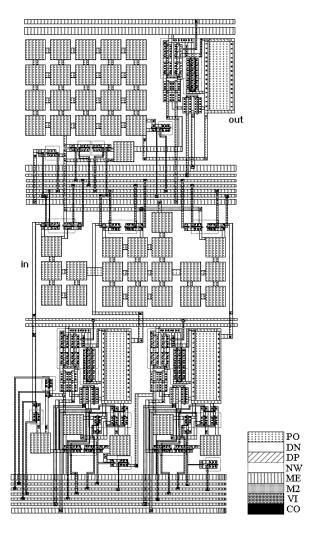

In the example projects, presented in the Fig.3.7 and 3.8, switches are realized as transmission gates, because of a small and almost constant on-resistance in contrast with switches realized as a single transistor. This, however, complicates the control of switches: two complementary clock signals (instead of a one) are necessary to control a single switch. This results in turn in the increment of the chip area, because the real number of clock phases (and also of respective connections) is doubled, i.e., is equal to 4 and not to 2.

The capacitors in the layouts presented in this subsection are realized as two plates: metal (ME) and polysilicon (PO) [5]. CC's are realized as parallel connections of many UC's. This makes it possible to keep the area-to-perimeter ratio constant [1].

#### 3.2.2 Chip area evaluation

The method for the approximate (theoretical) evaluation of the chip area, presented in Section 3.1 is based on the assumption that the area parameters  $S_{\rm OA}$ ,  $S_{\rm UC}$ ,  $S_{\rm CC}$ , and  $S_{\rm S}$  in the equation (3.1) are constant. In practice, this assumption is usually not exactly true. For instance, parameter  $S_{\rm CC}$ , which describes the area of the average coefficient

Table 3.14: Number of elements in cascaded delay-line structures

| Element       | Formula                                                     |  |

|---------------|-------------------------------------------------------------|--|

| OA            | $L_{\text{OA}} = 3(N \text{ div } 2) + 2(N \text{ mod } 2)$ |  |

| UC            | $L_{\rm UC} = 5(N \ {\rm div} \ 2) + 3(N \ {\rm mod} \ 2)$  |  |

| CC            | $L_{\rm CC} = 4(N \ {\rm div} \ 2) + 3(N \ {\rm mod} \ 2)$  |  |

| S             | $L_{\rm S} = 24(N \ {\rm div} \ 2) + 16(N \ {\rm mod} \ 2)$ |  |

| No. of phases | P=2                                                         |  |

capacitor, depends on the type of the filter frequency response and increases with the filter order N according to the following equation

$$S_{\rm CC}(N) = \frac{S_{\rm CT}(N)}{L_{\rm CC}(N)}.$$

(3.12)

For the delay-line structure No. 3 we get

$$S_{\rm CC}(N) = \frac{2(N+1)S_{\rm CM}}{N+2} \approx 2S_{\rm CM}$$

(3.13)

in the case of the DFT-type filter (i.e., for all coefficients  $h_i$  equal to each other) and

$$S_{\rm CC}(N) = \frac{2^{N+1}S_{\rm CM}}{N+2} \tag{3.14}$$

in the case of the Butterworth filter. The respective equations for the delay-line structure No. 2 are similar.

These two extreme examples show that the formulation of the chip area as a function of the filter order N only (i.e., as a single curve for the given order N) is not possible, because of a very high dispersion of  $S_{\rm CC}$ . In cascaded delay-line structures, however, this dispersion is much smaller. For Butterworth filters we even get a very simple relation  $S_{\rm CC} = 2S_{\rm CM}$ .

For the cascaded delay-line structures equations for computation of numbers of basic elements as functions of the filter order N are listed in Table 3.14. Constant coefficients occurring with expressions  $(N \operatorname{div} 2)$  and  $(N \operatorname{mod} 2)$  in Table 3.14 follow from equations given in Table 3.2 for N=2 (second order section) and N=1 (first order section), respectively.

The analysis presented so far still can be only used for the approximate evaluation of the chip area. It is due to the following facts:

- it is necessary to add some empty place between particular elements in the chip layout,

- we must remember that in reality we use the clock with complementary phases (i.e., with a doubled number of phases); this increases the required chip area,

- some parts of the chip area must be used for connections of the power supply and of the control signals such as  $V_{\rm DD}$ ,  $V_{\rm SS}$ ,  $V_{\rm ACT}$  and others,

- it is important to fulfil the design rules required for a particular technology: minimal layer dimensions, and spacing between particular layers exist, which have to be taken into account during the design process and cannot be omitted in the evaluation of the required chip area; in result, the clock path in reality is wider than that estimated in the third section,

- because CC's are realized as parallel connections of UC's, the area of a CC is a bit larger than that equal to the product of the UC area by the number of UC's it is because of some empty place necessary to leave between UC's.

It should also be stressed that if spacing between layers is too small, then the parasitic capacity will be unacceptably high. This also influences the required chip area.

For the cascaded delay-line structures the total (approximated) chip area can be computed using the following equation

$$S(N) = (3S_{\text{OA}} + 4S_{\text{CC}}(2) + 6S_{\text{UC}} + 26S_{\text{S}} + PS_{\text{C}}(2))(N \operatorname{div} 2) + + (2S_{\text{OA}} + 3S_{\text{CC}}(1) + 4S_{\text{UC}} + 17S_{\text{S}} + PS_{\text{C}}(1))(N \operatorname{mod} 2).$$

(3.15)

Coefficients  $S_{\rm C}(1)$  and  $S_{\rm C}(2)$  result from equation (3.2) for N=1 and N=2, respectively. Their estimates are:  $S_{\rm C}(1)=840~\mu{\rm m}^2$  and  $S_{\rm C}(2)=1080~\mu{\rm m}^2$ . Coefficients  $S_{\rm CC}(1)$  and  $S_{\rm CC}(2)$  should be computed according to equations (3.13), (3.14) for N=1 and N=2, respectively.

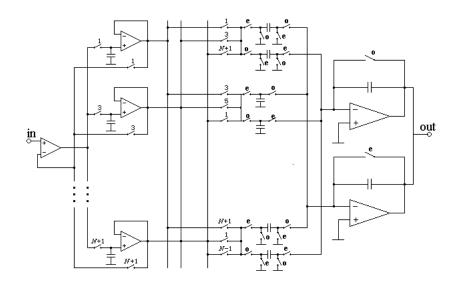

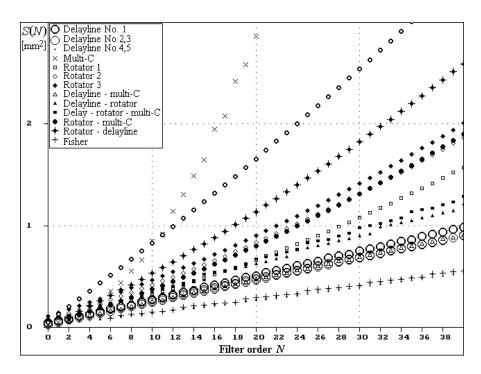

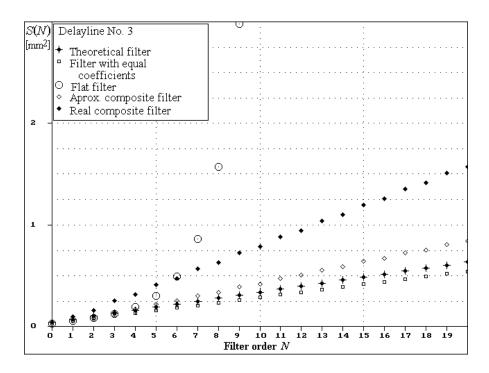

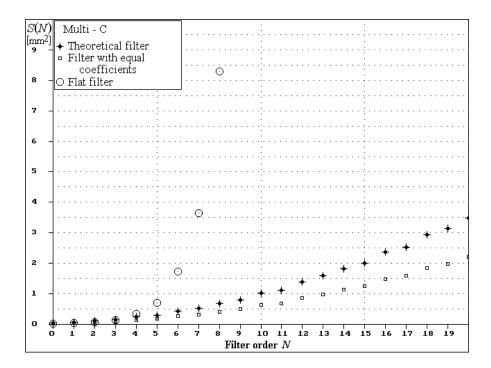

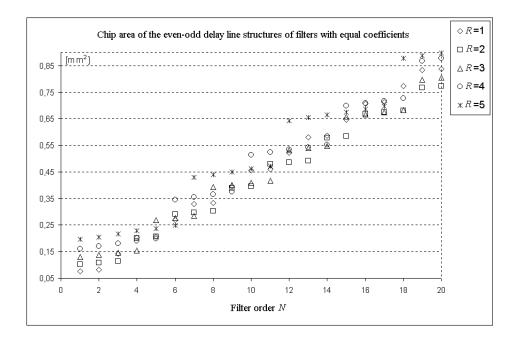

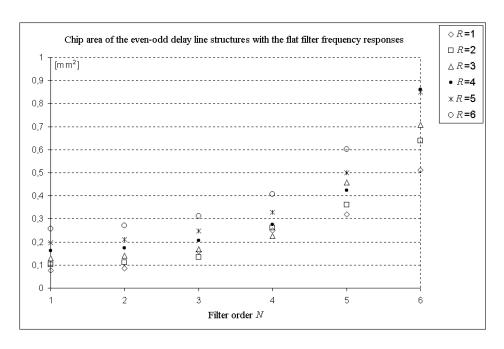

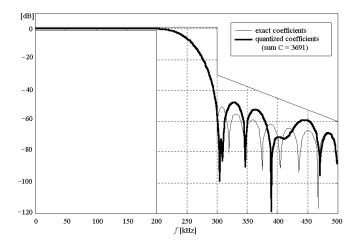

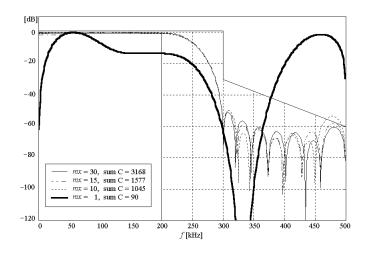

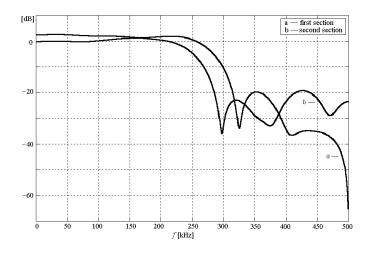

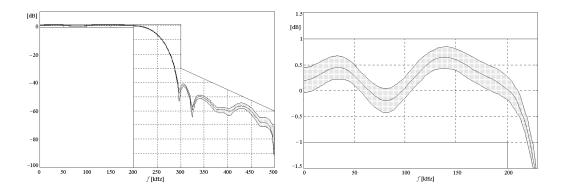

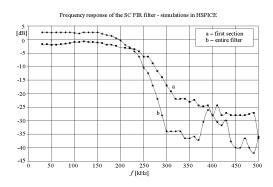

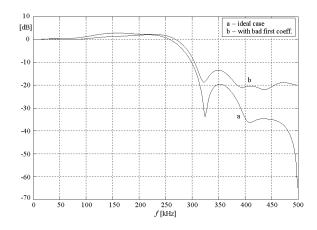

The plots of the chip area are depicted in the Figures 3.9 and 3.10 as functions of the filter order N for the delay-line structure No. 3 and for the multi-C structure, respectively. We do not present the results for the delay-line structure No. 2 because the chip area is in this case approximately equal to that obtained for the delay-line structure No. 3. Different curves are plotted and compared, including the approximated chip estimations described in Section 3.1 and the exact chip evaluation of real filters. The Butterwoth (flat) filters and the DFT-type (uniform coefficient filters) are treated as two "extreme" cases. Filters with uniform coefficients always require the smallest chip area because of no coefficient spread. In result, all coefficient capacitors (CC's) are small. For the flat filters, however, the coefficient spread is the highest among the cases considered and, in result, the chip area is the largest obtained. Thus, the characteristics of SC FIR filters of practical relevance lie inside the area between these two "extreme" curves.

In Figure 3.9 two additional, interesting curves are shown, corresponding to the cascade realization of the Butterworth filter (i.e., to the realization of the whole filter circuit as a cascade of second order sections and possibly of a single first order section occurring if the filter order is odd). The first curve is obtained by the approximate estimation using equation (3.15). The second one is exact and corresponds to the realization of

Figure 3.9: Chip area curves for the delay-line structure No. 3

Figure 3.10: Chip area curves for the multi-C structure

the integrated circuit. By the analysis of curves in Fig.3.9 it can be concluded that the cascade structure is the only reasonable solution for the FIR filters with a large coefficient spread, e.g., for the considered Butterworth filters. In contrast, for filters with uniform coefficients, the smallest chip area can be obtained using the direct delay-line structures.

## 3.3 Comparison of the SC FIR filter structures on the basis of the clock system criteria

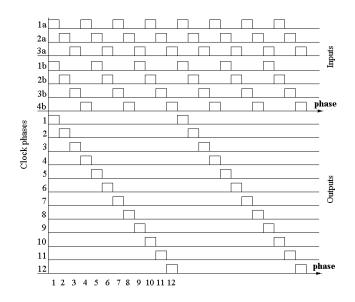

#### 3.3.1 Theoretical clock systems for particular SC FIR filters

In this Subsection theoretical clock systems for particular basic SC FIR filter structures are studied and evaluated. The word "theoretical" means that we do not take all practical aspects into account of the realization of a clock system. In practice, there exist various difficulties, which cause that the clock system is more complicated than in the theory. These aspects are considered in the next Subsection. Simplified (theoretical) analysis, given here, is an essential and indispensable basis for further analysis towards practical realization.

#### Delay line structure with Gillingham delay elements (No. 3)

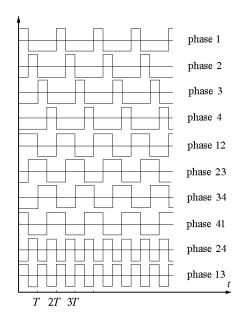

In this case only two clock phases are needed. An important advantage is that the number of the clock phases does not depend on the filter length N [1, 2, 33]. The clock system is very simple (see Figures 2.9 and 3.11). All switches in the structure are driven by only one clock phase.

Figure 3.11: Clock control in the delay line structure No. 3

#### Delay line (Fisher) structure (No. 4)

In this structure (see Figure 2.10) the number of clock phases is given by equation (3.16). It can be seen that this value depends on the filter order N. In structures of this kind, each clock phase must occur during the processing of a single sample.